**DSP HDL Toolbox**™

User's Guide

# MATLAB&SIMULINK®

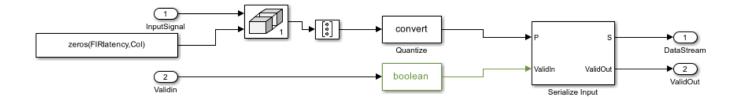

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

T

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

DSP HDL Toolbox™ User's Guide

© COPYRIGHT 2022-2023 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

#### **Revision History**

March 2022 Online only New for Version 1.0 (Release 2022a)

September 2022 Online only Revised for Version 1.1 (Release 2022b)

March 2023 Online only Revised for Version 1.2 (Release 2023a)

# Contents

|                                                                                                                                                                                                                                                                                                                                                                                                                                       | ples                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Align Parallel Data Streams                                                                                                                                                                                                                                                                                                                                                                                                           | 1-2                                                                  |

| HDL Implementation of LMS Filter                                                                                                                                                                                                                                                                                                                                                                                                      | 1-8                                                                  |

| High Performance DC Blocker for FPGA                                                                                                                                                                                                                                                                                                                                                                                                  | 1-21                                                                 |

| Frequency-Domain Filtering in HDL                                                                                                                                                                                                                                                                                                                                                                                                     | 1-30                                                                 |

| HDL Implementation of Four Channel Synthesizer and Channelizer                                                                                                                                                                                                                                                                                                                                                                        | 1-35                                                                 |

| Gigasamples-per-Second Correlator and Peak Detector                                                                                                                                                                                                                                                                                                                                                                                   | 1-43                                                                 |

| NFC Digital Downconverter                                                                                                                                                                                                                                                                                                                                                                                                             | 1-51                                                                 |

| Implement Digital Downconverter for FPGA                                                                                                                                                                                                                                                                                                                                                                                              | 1-66                                                                 |

| Implement Digital Upconverter for FPGA                                                                                                                                                                                                                                                                                                                                                                                                | 1-84                                                                 |

| implement Digital Opconverter for FFGA                                                                                                                                                                                                                                                                                                                                                                                                | 1-04                                                                 |

| HDL Optimized System De                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| HDL Optimized System De                                                                                                                                                                                                                                                                                                                                                                                                               | sign                                                                 |

| HDL Optimized System De                                                                                                                                                                                                                                                                                                                                                                                                               | sign<br>2-2                                                          |

| HDL Optimized System De  FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers                                                                                                                                                                                                                                                                                                                                            | sign<br>2-2<br>2-3                                                   |

| HDL Optimized System De  FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data                                                                                                                                                                                                                                                                                                                    | 2-2<br>2-3<br>2-5                                                    |

| HDL Optimized System De  FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture                                                                                                                                                                                                                                      | 2-2<br>2-3<br>2-5<br>2-6<br>2-6                                      |

| HDL Optimized System De  TR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture  Partly Serial Systolic Architecture (1 < N < L)                                                                                                                                                                                      | 2-2<br>2-3<br>2-5<br>2-6<br>2-6<br>2-7                               |

| HDL Optimized System De  FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture                                                                                                                                                                                                                                      | 2-2<br>2-3<br>2-5<br>2-6<br>2-6<br>2-7                               |

| FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture  Partly Serial Systolic Architecture $(1 < N < L)$ Fully Serial Systolic Architecture $(N \ge L)$                                                                                                                                                             | sign<br>2-2                                                          |

| FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture  Partly Serial Systolic Architecture $(1 < N < L)$ Fully Serial Systolic Architecture $(N \ge L)$                                                                                                                                                             | 2-2<br>2-3<br>2-5<br>2-6<br>2-6<br>2-7<br>2-8                        |

| HDL Optimized System De  FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture  Partly Serial Systolic Architecture (1 < N < L)  Fully Serial Systolic Architecture (N ≥ L)  High-Throughput HDL Algorithms  Blocks that Support Frame-Based Input  Hardware Control Signals                                        | 2-2<br>2-3<br>2-5<br>2-6<br>2-7<br>2-8                               |

| HDL Optimized System De  FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture  Partly Serial Systolic Architecture (1 < N < L)  Fully Serial Systolic Architecture (N ≥ L)  High-Throughput HDL Algorithms  Blocks that Support Frame-Based Input  Hardware Control Signals  Streaming Interface with Valid Signal | 2-2<br>2-3<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-9<br>2-12<br>2-12 |

| HDL Optimized System De  FIR Filter Architectures for FPGAs and ASICs  Complex Multipliers  Frame-Based Input Data  Fully Parallel Systolic Architecture  Fully Parallel Transposed Architecture  Partly Serial Systolic Architecture (1 < N < L)  Fully Serial Systolic Architecture (N ≥ L)  High-Throughput HDL Algorithms  Blocks that Support Frame-Based Input  Hardware Control Signals                                        | 2-2<br>2-3<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-9                 |

| _ |

|---|

| 3 |

| • |

| _ |

|          | Generate Sine Wave                                       | 3-2        |

|----------|----------------------------------------------------------|------------|

|          | Fully Parallel Systolic FIR Filter Implementation        | 3-5        |

|          | Partly Serial Systolic FIR Filter Implementation         | 3-9        |

|          | Optimize Programmable FIR Filter Resources               | 3-13       |

|          | FIR Decimation for FPGA                                  | 3-18       |

|          | Implement atan2 Function for HDL                         | 3-20       |

|          | Downsample a Signal                                      | 3-23       |

|          | Control Data Rate Using Ready Signal                     | 3-26       |

|          | Automatic Delay Matching for the Latency of FFT Block    | 3-29       |

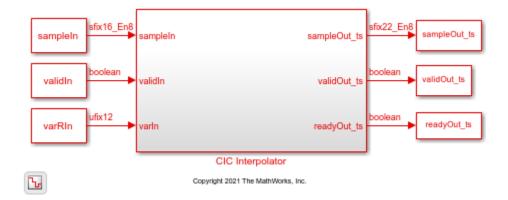

|          | Implement CIC Interpolator Filter for HDL                | 3-31       |

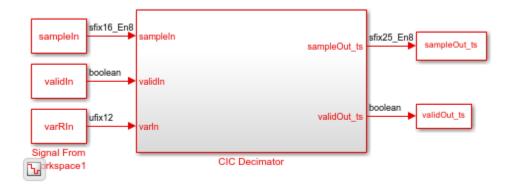

|          | Implement CIC Decimator Filter for HDL                   | 3-34       |

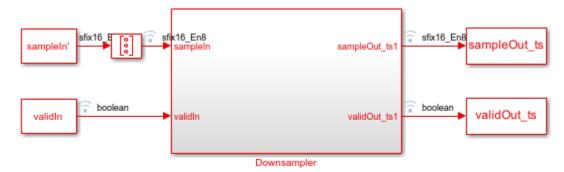

|          | Implement Downsampler For HDL                            | 3-37       |

|          | Implement Upsampler for HDL                              | 3-39       |

|          | Calculate Mean Square Error Performance Using LMS Filter | 3-41       |

|          |                                                          |            |

|          | HDL Code Generation and Deployn                          | nent       |

| 4        |                                                          |            |

|          | Prototype DSP HDL Algorithms on Hardware                 | 4-2<br>4-2 |

| <b>F</b> | Radar Application Exam                                   | ples       |

| <b>5</b> |                                                          |            |

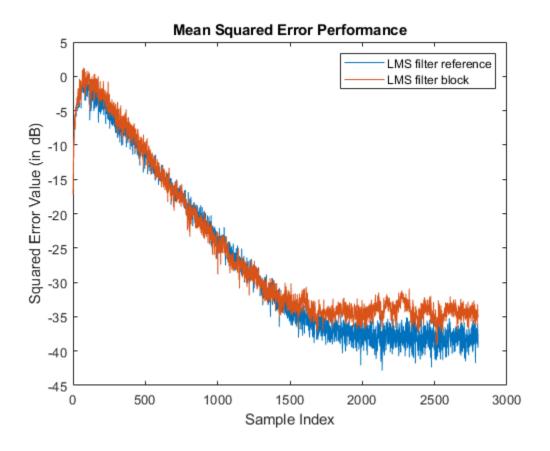

|          | FPGA-Based Beamforming in Simulink: Algorithm Design     | 5-2        |

|          | FPGA-Based Beamforming in Simulink: Code Generation      | 5-9        |

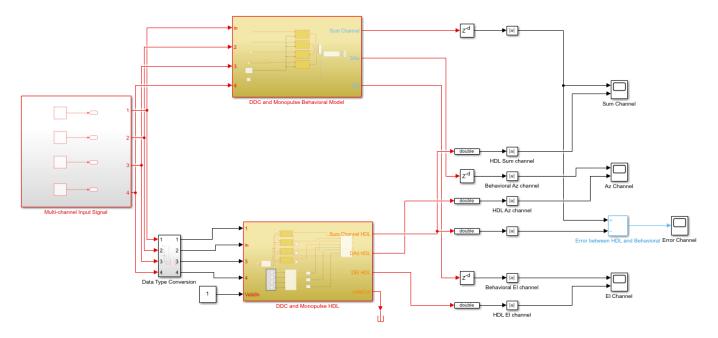

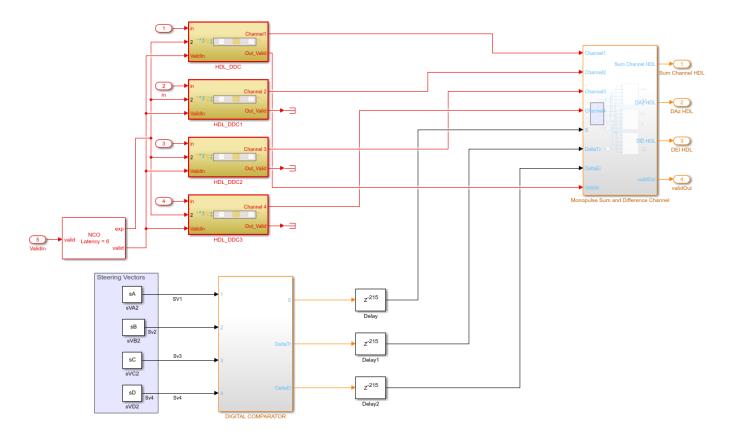

|          | FPGA-Based Monopulse Technique: Algorithm Design         | 5-16       |

|          | FPGA-Based Monopulse Technique: Code Generation          | 5-27       |

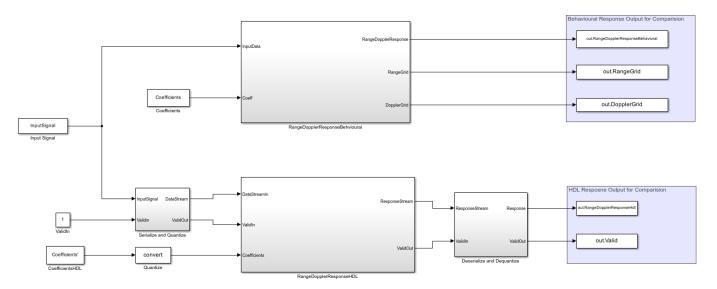

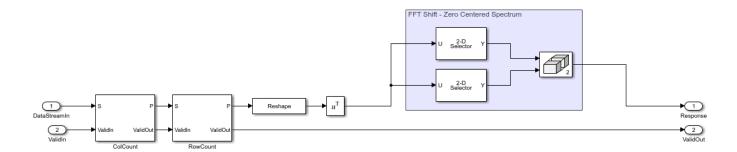

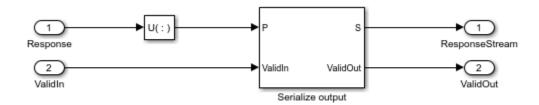

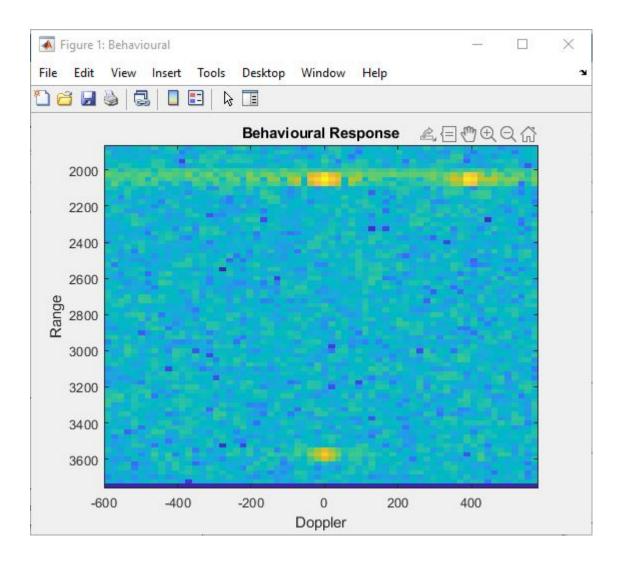

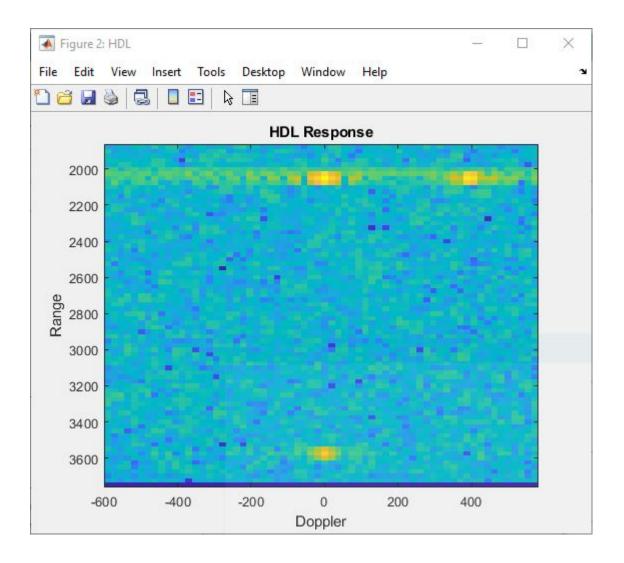

| FPGA-Based Range-Doppler Processing - Algorithm Design and HDL Cod<br>Generation | le<br>5-36 |

|----------------------------------------------------------------------------------|------------|

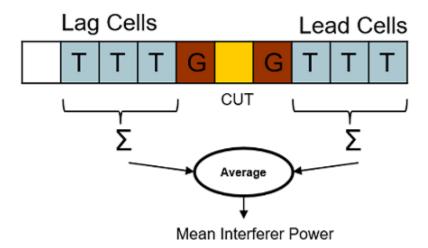

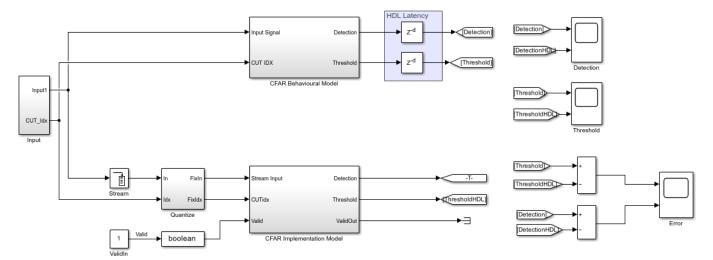

| FPGA-Based Cell-Averaging Constant False Alarm Rate (CA-CFAR)  Detector          | 5-54       |

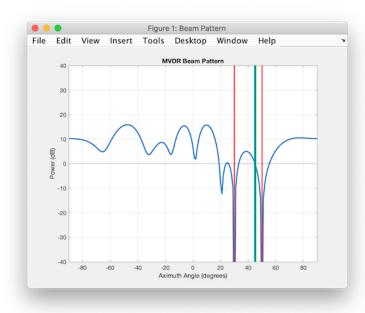

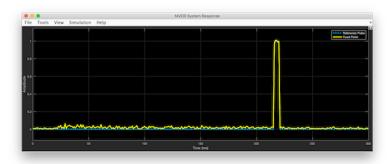

| FPGA-Based Minimum-Variance Distortionless-Response (MVDR) Beamformer            | 5-68       |

# **Featured Examples**

- "Align Parallel Data Streams" on page 1-2

- "HDL Implementation of LMS Filter" on page 1-8

- "High Performance DC Blocker for FPGA" on page 1-21

- "Frequency-Domain Filtering in HDL" on page 1-30

- $\bullet$  "HDL Implementation of Four Channel Synthesizer and Channelizer" on page 1-35

- "Gigasamples-per-Second Correlator and Peak Detector" on page 1-43

- "NFC Digital Downconverter" on page 1-51

- "Implement Digital Downconverter for FPGA" on page 1-66

- "Implement Digital Upconverter for FPGA" on page 1-84

## **Align Parallel Data Streams**

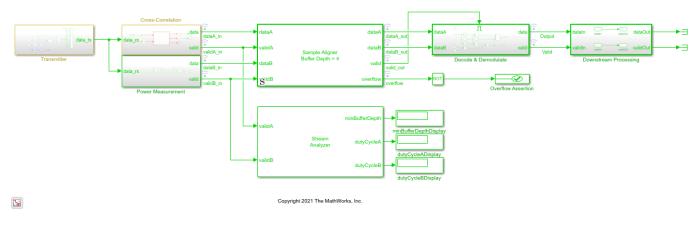

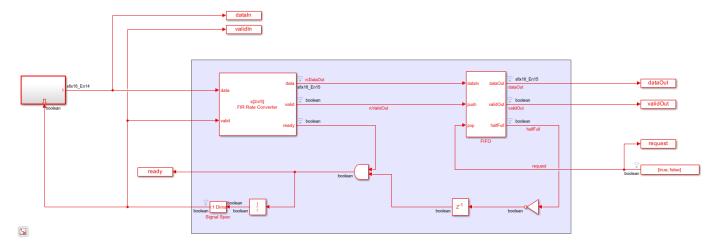

This example shows how to align two commonly sourced data streams with different upstream operation latencies using FIFO-based buffering.

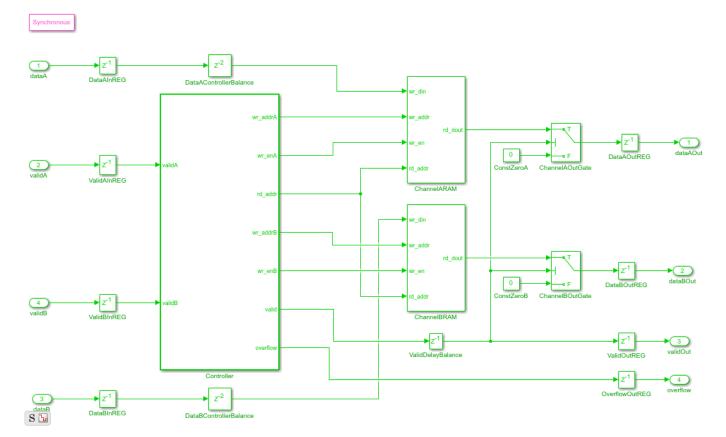

In this example we use the SampleAligner to align two data streams relative to their valid signals. The SampleAligner subsystem uses FIFOs with synchronized read operations. This implementation works only if the input streams have the same number of valid samples in a time period.

The model generates a random Barker-encoded BPSK input data stream that simulates data from a transmitter. The implemented Barker decoder requires computing the cross-correlation and signal power, and then using those two signals to decode the transmitted samples. Two parallel subsystems perform cross-correlation and measure the signal power. These operations have different latencies, so to recombine the two data streams, they must be re-aligned. The cross-correlation and power measurement operations also do not change the rate or duty cycle of the shared input stream, so they are suitable for a FIFO implementation.

| ►dataA_in | O | (-1         | <u> </u>      | <u> </u>  | -1 | (11 )(-1 |  |

|-----------|---|-------------|---------------|-----------|----|----------|--|

| validA_in |   |             |               |           |    |          |  |

| ▶dataB_in | 0 | (1 (2 (3 (4 | (5 (6 (7 (8 ( | 9 (10)(11 |    |          |  |

| validB_in |   |             |               |           |    |          |  |

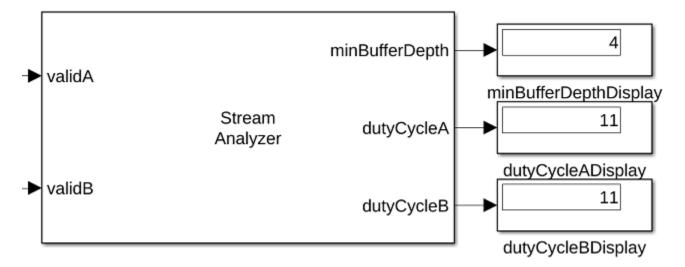

#### **Stream Analyzer**

To align the data streams the required buffer depth must be determined and the duty cycle of the data streams be verified as being equal. This is achieved using the StreamAnalyzer which accepts the valid signals of two data streams and determines these required parameters.

- The **minBufferDepth** output determines the minimum number of samples that must be buffered to synchronize the data streams. This value is determined by taking the maximum modulus value of a counter which is incremented on a valid from stream A and decremented on a valid from stream B.

- The dutyCycleA and dutyCycleB outputs provide the number of valid samples per second. This calculation starts counting valid samples when it receives the first valid sample on each input stream. The StreamAnalyzer's block sample time is used as the signal period when determining the dutyCycle. The duty cycle of both data streams must match to ensure that the internal buffer of the SampleAligner do not overflow. The length of the simulation affects the results of each channel's duty cycle. Longer simulations give more accurate representations of the duty cycles.

The StreamAnalyzer is for use in simulation only and does not support HDL code generation.

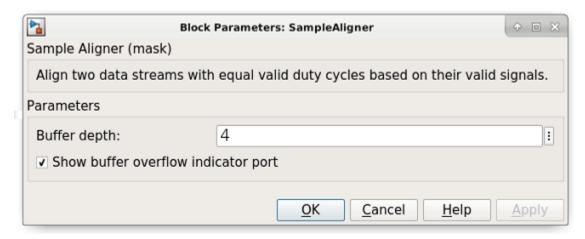

#### **Sample Aligner**

The SampleAligner masked subsystem aligns the samples of two data streams based on their respective valid signals. The subsystem buffers incoming data from either stream until there is at least one valid sample stored from both streams, and then reads both buffers to return a sample for each data stream. The SampleAligner requires that the valid duty cycle of the input data streams match to prevent internal buffer overflows.

The buffer depth parameter sets the internal sample buffer depths. This parameter can be determined from analysis of the latencies for each data stream or from the use of the StreamAnalyzer. The implemented buffer depth is equal to 2^nextpow2(bufferDepth + 5). The extra 5 samples accounts for internal control logic latency when operating with continuous valid data streams.

The SampleAligner can be configured to provide an overflow indicator output port which will return a true Boolean value if either of the buffers experience an overflow. In the event of an overflow, no new data is written to the full buffer. This condition leads to loss of data integrity after the buffered samples have been output.

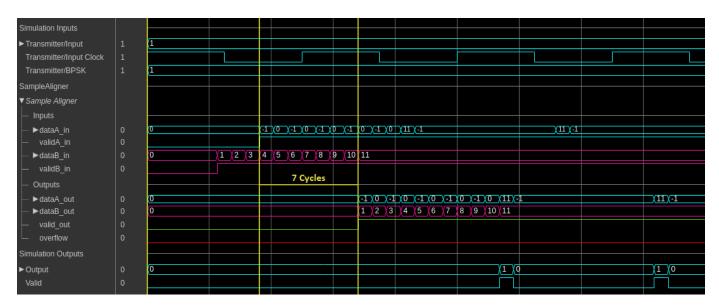

The SampleAligner architecture supports high clock rate applications with its frequency limit imposed by the inferred RAM type. This pipelining means the SampleAligner has a write-to-read latency of 7 clock cycles and a 4 clock cycle latency for the output of an overflow indicator. The input data types for each separate stream does not have to match. Both input streams must be scalar values.

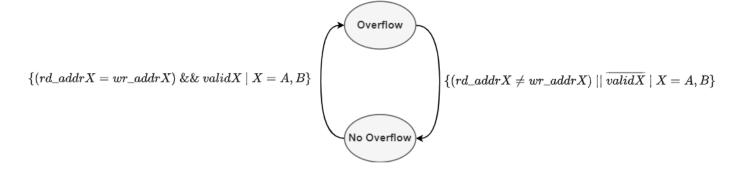

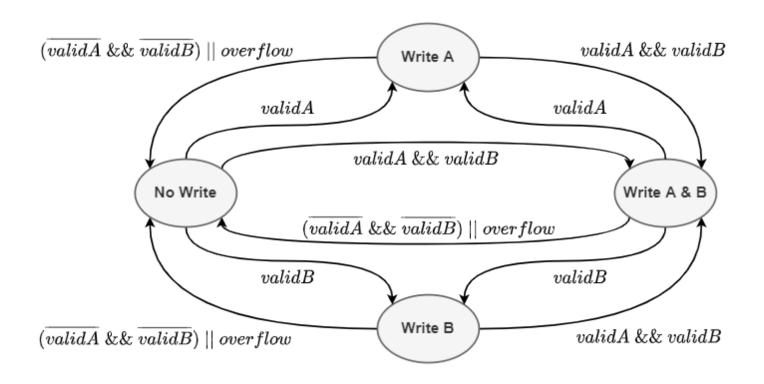

The SampleAligner Controller consists of three parallel operations which handle write and read operations. Pseudo code for these operations are shown below, with more in-depth state diagrams found at the end of example.

```

if (valid_A)

if (BufferNotFull_A)

write_A();

else

overflow();

end

end

```

```

if (valid_B)

if (BufferNotFull_B)

write_B();

else

overflow();

end

end

if (BufferNotEmpty_A) && (BufferNotEmpty_B)

read();

end

```

#### **Considerations for Stream Aligning**

Performing alignment of parallel data streams is highly specific to the intended use case. The processing applied to both streams prior to the desired alignment stage as well as the downstream processing must be considered to define the alignment constraints. An equal valid duty cycle across both data streams allows for simple FIFO-based buffering. A difference in the valid duty cycles needs to be carefully handled based on the specific use case and may not be possible. Any rate changes across the data streams and the impact of filter architectures on the valid signal must be accounted for. Two data streams can have an equal duty cycle yet different pacing. One could be regular and the other could be a dense bursty stream of data. Bursty data would require a deeper buffer to ensure proper alignment. The present control signals must also be considered, with the introduction of start and end signals imposing additional alignment requirements, deeper buffers, and extended control logic.

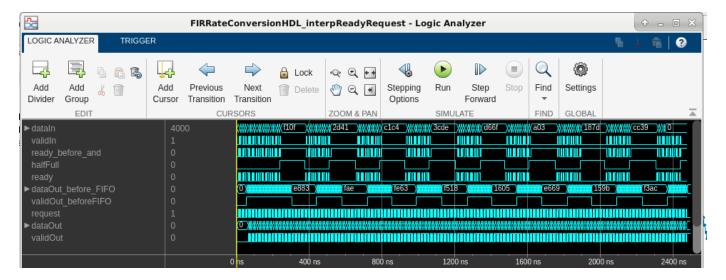

#### **Simulation Results**

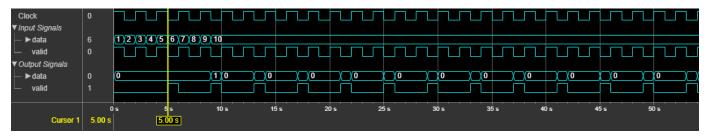

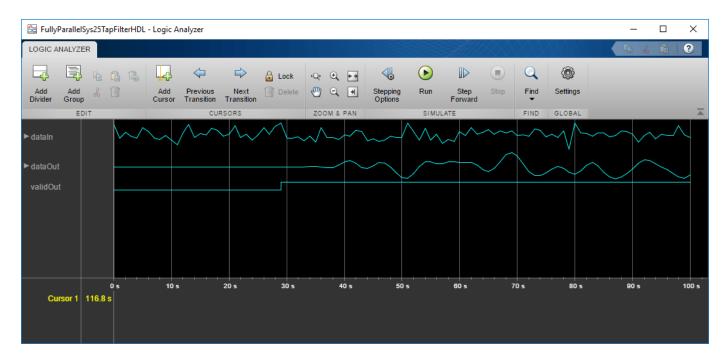

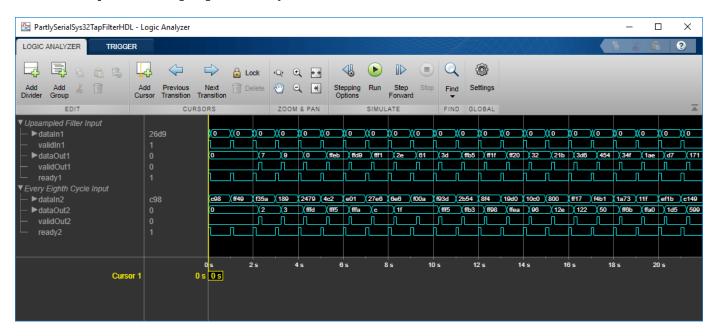

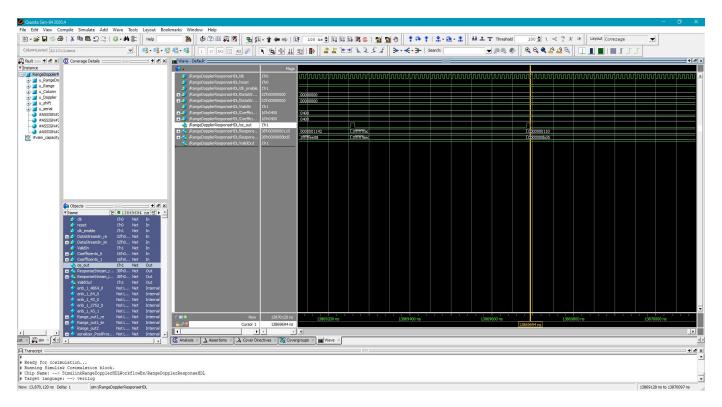

The resulting simulation waveforms can be observed using the Logic Analyzer and show the SampleAligner ensure that both data streams are synchronously output.

#### **HDL Implementation Results**

The generated HDL code for the SampleAligner subsystem was synthesized for a Xilinx™ Zynq-7000 ZC706 board and met timing constraints of 649 MHz. The required resources are shown in the table.

T =

3x2 table

Resource Usage

LUT 39

LUTRAM 8

Flip Flop 99

To check and generate the HDL code referenced in this example, you must have the HDL Coder™ product. To generate the HDL code, use this command.

makehdl('SampleAlignment/StreamAligner')

In addition to the HDL generated for this example, the SampleAligner met timing constraints on a Xilinx™ Zynq-7000 ZC706 of 649 MHz and 457 MHz for buffer depths which inferred DRAM and BRAM respectively when operating with two 16-bit data streams. The inferred RAM type is dependent on the implemented buffer size. The SampleAligner controller can see its pipelining reduced or removed to reduce the write-to-read latency if operating at lower frequencies.

#### **Sample Aligner Controller Architecture**

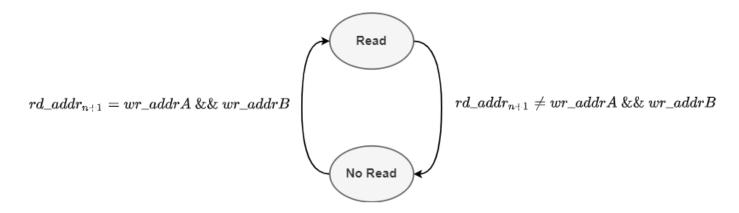

The following state diagrams provide a more in-depth description of the SampleAligner's controller operation.

#### See Also

#### **More About**

"Hardware Control Signals" on page 2-12

## **HDL Implementation of LMS Filter**

This example shows how to implement a fully serial and transpose delayed least mean square (LMS) adaptive filters. The fully serial LMS filter uses standard LMS adaptive filter algorithm and the transpose delayed LMS filter uses delayed LMS filter algorithm with a transpose filter architecture. You can use the fully serial LMS filter for low data-rate applications, such as audio and speech, and the transpose delayed LMS filter for high throughput applications in wireless communication. For high throughput applications, you can also use the LMS Filter block in DSP HDL Toolbox $^{\text{TM}}$ . The Simulink $^{\text{RM}}$  model in this example is optimized for HDL code generation and hardware implementation.

The fully serial and transpose delayed LMS filters minimize the error between a desired signal and an observed signal by adjusting the filter weights using mean square error (MSE) criteria. The example model accepts observed, desired, and step-size signals as input and computes the filtered signal, filter error, and filter weights or coefficients. You can use LMS filters for system identification, inverse system identification, noise cancelation, and prediction.

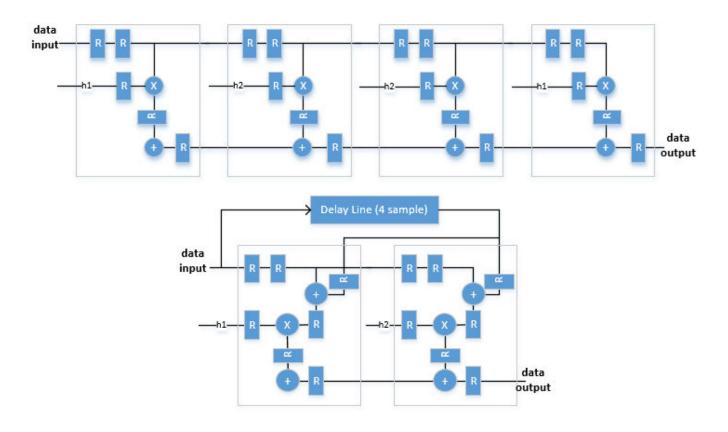

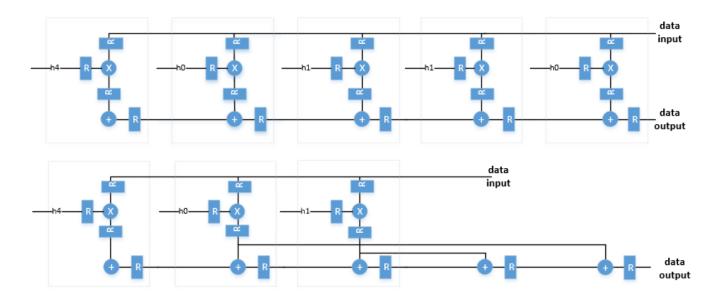

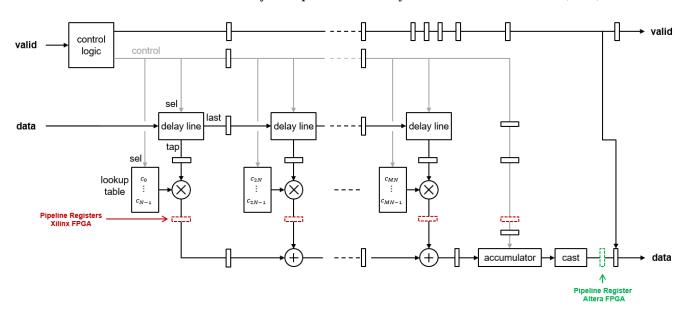

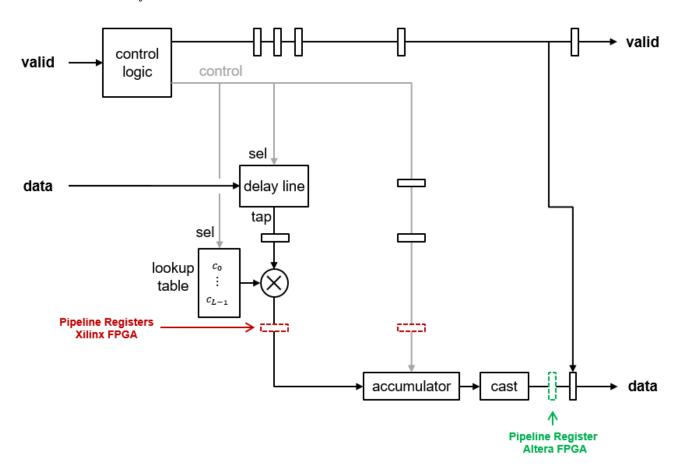

#### **Fully Serial LMS Filter**

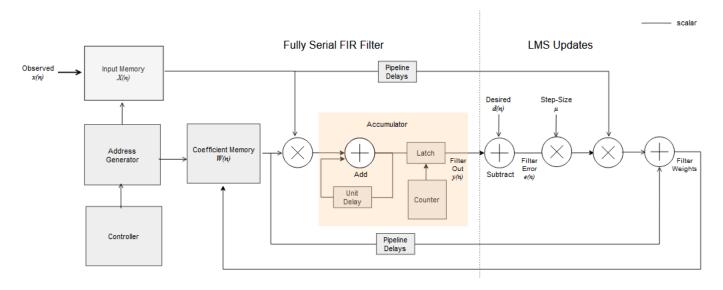

The block diagram in this section explains the implementation of a fully serial finite impulse response (FIR) filter architecture along with the LMS algorithm filter weights. In this block diagram, the buffered input samples select the data for each tap serially and multiplies with the corresponding coefficients. This architecture reduces the hardware resource utilization, which generates less number of multipliers with additional logic elements such as multiplexers and registers, when compared to fully parallel implementation of LMS filter. Implementation of this architecture requires a clock rate that is faster than the input sample, which depends on the filter length and the number of delays in the feedback path. For example, for a filter length of 16, the block accepts valid input samples for every 35 clock cycles, which is the filter length plus 19 clock cycles.

This section explains the LMS equations corresponding to this architecture. The observed signal x(n) is passed as an input to the filter and buffered for every filter length of samples. This buffered data X(n) is multiplied serially with the corresponding filter coefficients  $W_n$  and accumulated in a register to get the filtered output y(n) at timestep n.

$$y\left(n\right) = W_{n}^{T}X\left(n\right)$$

To get the filter error output at timestep n, subtract the filtered output y(n) from the desired signal d(n)

$$e(n) = d(n) - y(n)$$

To update the LMS filter weights  $W_n$  for the next timestep n+1, LMS uses the filter error e(n) and step size  $(\mu)$ .

$$W_{n+1} = W_n + \mu e(n) X^*(n)$$

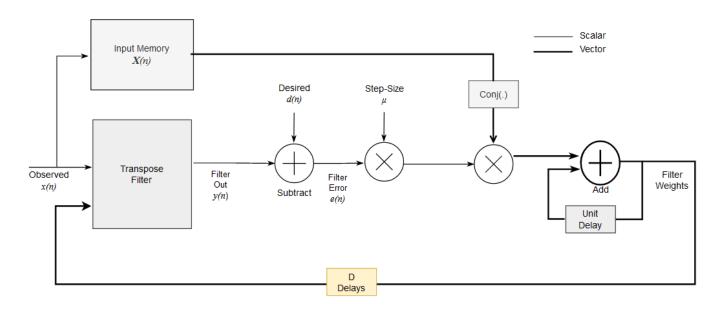

This architecture diagram consists of the fully serial FIR part, y(n) and the LMS update part, e(n) and  $W_{n+1}$ . The left-side of the diagram shows the fully serial FIR part, and the right-side of the diagram shows the LMS filter weight update part. The input and coefficient memories are used to buffer the observed data and store the filter coefficients.

#### **Model Architecture**

Open the example model by entering this command at the MATLAB® command prompt.

```

modelname = 'HDLFullySerialLMSModel';

open_system(modelname);

```

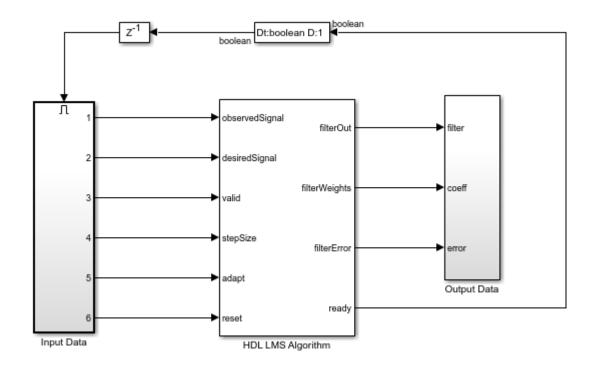

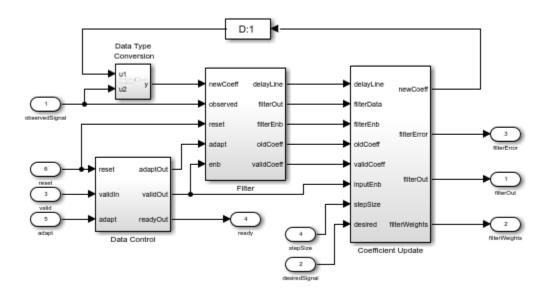

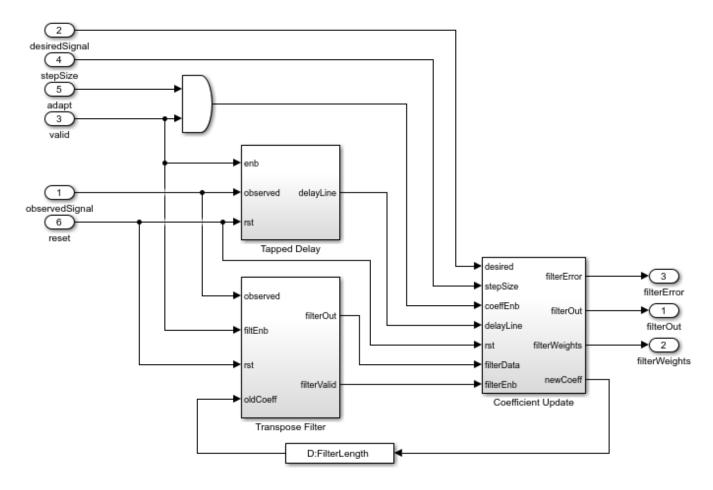

The HDL LMS Algorithm subsystem has Data Control, Filter, and Coefficient Update blocks. The Data Control block generates control signals to control the flow of data. The ready signal indicates when to provide the next valid data. The Filter block implements the serial FIR filter and writes the observed input samples to the RAM. The control logic reads the buffered data serially in such a way

that these samples get multiplied with their corresponding filter weights and that the output product is added serially to a register for every filter length of samples to get the filtered output. The Filter block stores the LMS filter weight updates in the RAM and resets the block using a separate reset control logic (when required). The Coefficient Update block implements e(n) and  $W_{n+1}$  of the LMS filter. This example starts with a set of zeros as initial values for the estimates of the filter weights.

open system([modelname '/HDL LMS Algorithm'], 'force')

#### **Transpose Delayed LMS Filter**

This section explains the equations corresponding to the delayed LMS algorithm. These equations are approximations to the standard LMS algorithm. The transpose delayed LMS filter uses these equations with transpose filter structure to fit the hardware characteristics. The observed signal x(n) is passed as an input to the filter. The number of delays (D) in the feedback path are independent of filter length because the filter part is implemented using a transposed filter architecture, which improves the throughput by minimizing the pipelined delays in the feedback path of LMS filter.

The filtered output y(n) at timestep n is given by the equation.

$$y\left(n\right) = W_{n-D}^{T}X\left(n\right)$$

To get the filter error output at timestep n, subtract the filtered output y(n) from the desired signal d(n)

$$e\left(n\right) = d\left(n\right) - y\left(n\right)$$

To update the filter weights  $W_n$  for the next timestep n+1, LMS filter uses the filter error  $e^{(n)}$  and step size  $(\mu)$ .

$$W_{n+1} = W_n + \mu e(n) X^*(n)$$

This architecture diagram shows the transpose delayed LMS filter.

#### **Model Architecture**

Open the example model by entering this command at the MATLAB® command prompt.

```

modelname = 'HDLDelayedLMSModel';

open_system(modelname);

```

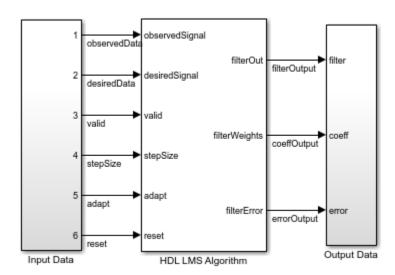

The HDL LMS Algorithm subsystem has Transpose Filter, Tapped Delay, and Coefficient Update blocks. The Transpose filter implements the transpose filter structure and outputs y(n). The Tapped delay block buffers the input data X(n). The Coefficient Update block implements e(n) and  $W_{n+1}$  of the LMS filter. This example starts with a set of zeros as initial values for the estimates of the filter weights.

```

open_system([modelname '/HDL LMS Algorithm'],'force')

```

#### **Port and Parameter Descriptions**

This section explains the port and parameter descriptions for the HDLFullySerialLMSModel.slx and HDLDelayLMSFilterModel.slx models. The input observedSignal and desiredSignal signals must be scalars and of the same data type. To support HDL code generation, inputs must be scalar fixed-point data types.

#### **Input Ports**

- **observedSignal** Input observed signal x(n) to the LMS filter, specified as a real- or complex-valued scalar. The block supports double, single, and signed fixed-point data types.

- **desiredSignal** Input desired signal d(n) to the LMS filter, specified as a real- or complex-valued scalar. The block supports double, single, and signed fixed-point data types.

- **stepSize** Input step size  $\mu$  to the block, specified as **double**, **single**, or unsigned fixed-point data types. This value determines the convergence rate and stability of the filter and must be less than 1/(power of input signal x filter length) for filter stability. For more information, see [1].

- **reset** Input reset signal, specified as a Boolean scalar. When **reset** is true, the block stops the current calculation and clears the internal states.

- valid Input valid signal, specified as a Boolean scalar to validate the input data.

• **adapt** — Input adapt signal, specified as a Boolean scalar. When this signal is 1 (high), the LMS filter updates its filter weights. When this signal is 0 (low), the filter weights remain the same as what they were previously. This signal is sampled only when the valid signal is 1 (high).

#### **Output Ports**

- **fiteredOut** Filtered output y(n), returned as a scalar. The LMS filter converges this signal with desired signal d(n) by adjusting filter weights.

- **filterError** Filter error e(n), returned as a scalar. This value is the difference between filtered output y(n) and desired signal d(n).

- filterWeights Filter weights  $W_n$ , returned as a scalar for the HDLFullySerialLMSModel.slx model and a vector of the same size as filter length for the HDLDelayLMSFilterModel.slx model.

- **ready** Ready signal, returned as a Boolean scalar. This port is applicable for the HDLFullySerialLMSModel.slx model. This signal indicates when to provide the next data.

This LMS filter model accepts the filter length as a parameter.

For a fixed-point implementation, internal word length calculations are based on the assumption that the input is a unit power signal. The recommended data type for the inputs and the observed and desired signals is fixdt(1,16,14). The recommended data type for the step size is fixdt(0,18,18).

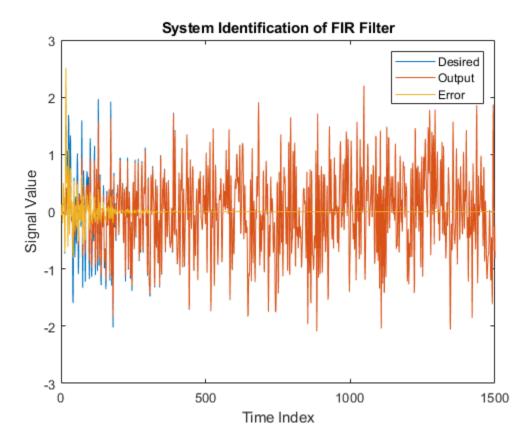

#### **System Identification of FIR Filter**

System identification is a process to find unknown system filter coefficients using an adaptive filter. This section shows how to find unknown system coefficients.

Create a filter object for an unknown system.

#### Specify a model.

```

% For the fully serial LMS filter, use 'HDLFullySerialLMSModel', for

% delayed LMS filter use 'HDLDelayedLMSModel'

modelname = 'HDLFullySerialLMSModel';

```

Pass the unit power signal, observedSignal to the FIR filter. The desiredSignal is the sum of the output of the unknown system (FIR filter) and the additive noise signal noise. The LMS filter adapts its coefficients until its transfer function matches the transfer function of the unknown system.

```

observedSignal = randn(1500,1);

noise = 0.001*randn(1500,1);

desiredSignal = filterObj(observedSignal) + noise;

stepSize = 0.01;

% Create input and control signals

adaptIn = true(length(observedSignal),1);

resetIn = false(length(observedSignal),1);

validIn = true(length(observedSignal),1);

if strcmpi(modelname, 'HDLFullySerialLMSModel')

simtime = length(observedSignal)*(filterLength+19) + 10;

else

simtime = length(observedSignal) + 100;

end

out = sim(modelname);

% Capture valid data outputs

actFilterOut = out.filterOut;

actCoeffOut = out.coeffOut:

actErrorOut = out.errorOut;

Plot the outputs.

figure;

plot(1:1:length(observedSignal),double([desiredSignal,actFilterOut,actErrorOut]))

title('System Identification of FIR Filter')

legend('Desired','Output','Error')

xlabel('Time Index')

ylabel('Signal Value')

```

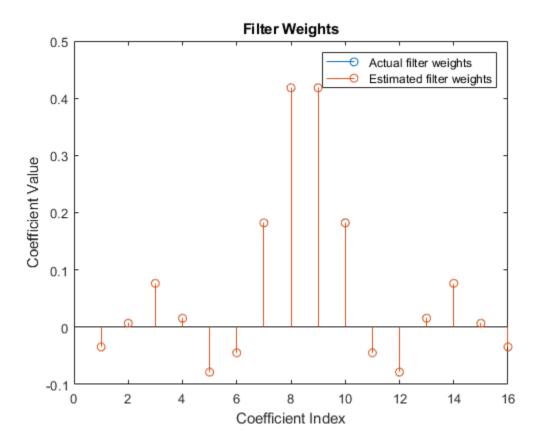

Because the output weights for the HDLFullySerialLMSModel.slx model are serial, you must convert the weights to a vector to represent the coefficients of the LMS filter, which is adapted to resemble the unknown system (FIR filter). To confirm the convergence, compare the numerator of the FIR filter with the estimated weights of the LMS filter.

```

figure;

```

```

% Compare actual filter weights with estimated filter weights

if strcmpi(modelname, 'HDLFullySerialLMSModel')

val = (filterLength)*(length(observedSignal)-1);

stem([(filterObj.Numerator).' double(actCoeffOut((val+1):(val+filterLength)))]);

else

val = (length(observedSignal)-1);

stem([(filterObj.Numerator).' double(actCoeffOut((val+1),:)).']);

end

xlabel('Coefficient Index')

ylabel('Coefficient Value')

title('Filter Weights')

legend('Actual filter weights','Estimated filter weights', ...

'Location','NorthEast')

```

#### **Verification and Results**

For verification, compare the outputs from this example with the outputs from the dsp.LMSFilter function.

```

lms = dsp.LMSFilter(filterLength, 'StepSize', stepSize);

[y,e,w] = lms(observedSignal, desiredSignal);

```

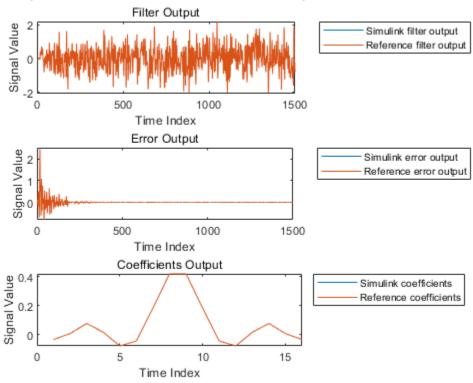

Plot the Simulink and reference outputs and verify the difference between them.

```

figure;

```

```

% Compare Simulink and reference filtered out

subplot(3,1,1)

plot(1:length(observedSignal),[actFilterOut,y])

title('Comparision Between Simulink and Reference Outputs')

subtitle('Filter Output')

legend('Simulink filter output', 'Reference filter output', 'Location', 'bestoutside')

xlabel('Time Index')

ylabel('Signal Value')

% Compare Simulink and reference filter error out

subplot(3,1,2);

plot(1:length(observedSignal),[actErrorOut,e])

subtitle('Error Output')

legend('Simulink error output', 'Reference error output', 'Location', 'bestoutside')

xlabel('Time Index')

ylabel('Signal Value')

```

```

% Compare Simulink and reference filtered coefficients

subplot(3,1,3);

if strcmpi(modelname, 'HDLFullySerialLMSModel')

plot(1:filterLength,[double(actCoeffOut((val+1):(val+filterLength))),w])

else

plot(1:filterLength,[double(actCoeffOut((val+1),:)).',w])

end

subtitle('Coefficients Output')

legend('Simulink coefficients','Reference coefficients','Location','bestoutside')

xlabel('Time Index')

ylabel('Signal Value')

```

#### Comparision Between Simulink and Reference Outputs

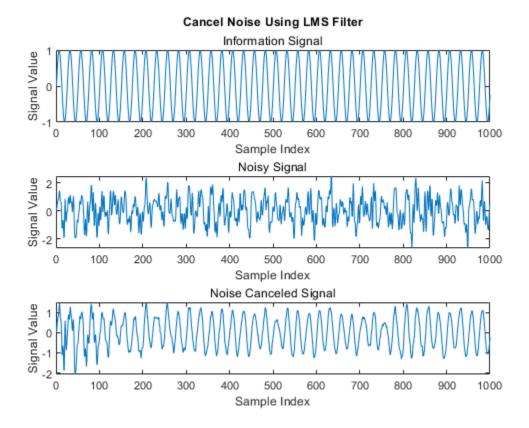

#### **Noise Cancellation Using LMS Filter**

Run the HDLLMSNoiseRemoval.m script to remove noise from the information signal. The information signal is a pure sine wave corrupted with additive noise, which is considered as a desired signal. The observed signal is correlated with noise data and fed to the LMS filter. When the filter converges, it provides the noise-canceled information signal from the **filterError** port. This plot shows the information signal, noisy signal, and the output noise corrected signal from the fully serial LMS filter in the HDLFullySerialLMSModel.slx model. You can generate similar plot for the transpose delayed LMS filter by specifying the model HDLDelayedLMSModel.slx in the HDLLMSNoiseRemoval.m script.

#### >> HDLLMSNoiseRemoval

**HDLLMSNoiseRemoval**

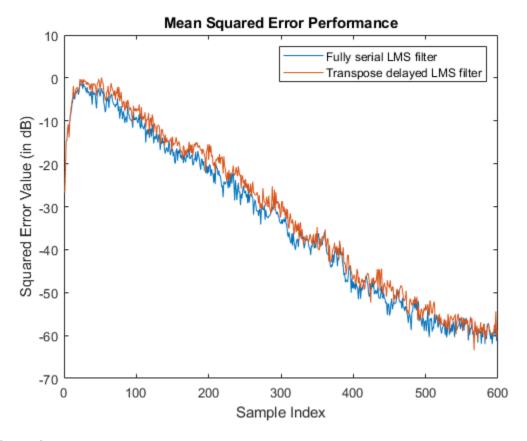

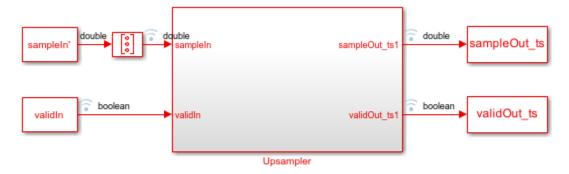

#### **Mean Square Performance**

Run the HDLLMSConvergencePlot.m script to plot the mean square error (MSE) performance of the LMS algorithm. The MSE measures the average squares of the errors between the desired signal and the primary input signal to the adaptive filter. This plot is the convergence plot for the fully serial LMS filter in the HDLFullySerialLMSModel.slx model and the transpose delayed LMS filter in the HDLDelayedLMSModel.slx model. The convergence plot of the transpose delayed LMS filter for the small step sizes closely matches with the fully serial LMS filter.

>> HDLLMSConvergencePlot

**HDLLMSConvergencePlot**

#### **Throughput**

The throughput for the fully serial LMS filter in the HDLFullySerialLMSModel.slx model is calculated as (fMax / (FL + t)). The throughput for transpose delayed LMS filter in the HDLDelayedLMSModel.slx model is equivalent to fMax, which is independent of the filter length. In this calculation: fMax is the maximum operating frequency, FL is the filter length, and t is the number of pipeline delays required in feedback path of fully serial LMS implementation. t is 19 in this implementation.

#### **HDL Code Generation and Implementation Results**

To generate HDL code for this example, you must have HDL Coder<sup>™</sup> product. To generate HDL code and HDL test bench, use the makehdl and makehdltb commands. The block is synthesized on a Xilinx® Zynq®-7000 ZC706 evaluation board.

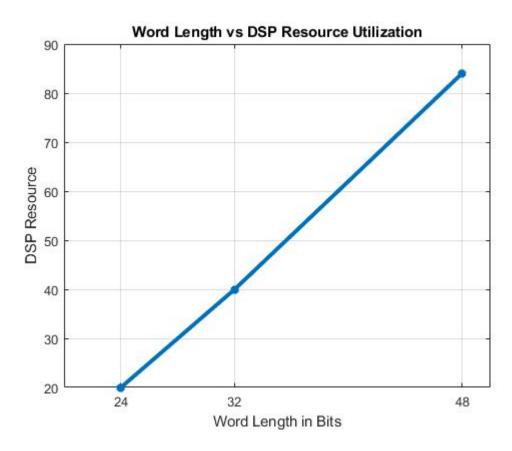

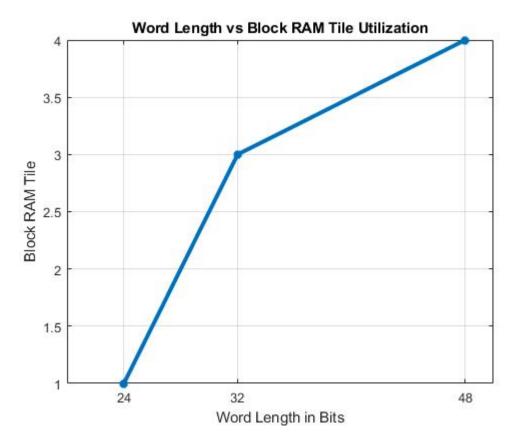

For the fully serial LMS filter in the HDLFullySerialLMSModel.slx model, this example achieves a clock frequency of 470 MHz. For the transpose delayed LMS filter in the HDLDelayedLMSModel.slx model, this example achieves a clock frequency of 450 MHz. These tables show the post place and route resource utilization results for the real-valued input word length of 16 and step-size word length of 18 for a filter length of 16 for both models. The resource utilization and synthesis frequency vary with the filter length and input word lengths.

Display the resource utilization for the fully serial LMS filter in the HDLFullySerialLMSModel.slx model.

```

F = table( ...

categorical({'Slice Registers'; 'Slice LUT';'DSP'}), ...

```

```

categorical({'551'; '412'; '3'}), ...

categorical({'437200'; '218600'; '900'}), ...

categorical({'0.13'; '0.19'; '0.33'}), ...

'VariableNames',{'Resources','Utilized','Available','Utilization (%)'});

disp(F)

Resources Utilized Available Utilization (%)

```

| Resources       | Utilized | Available | Utilization (%) |

|-----------------|----------|-----------|-----------------|

| Slice Registers | 551      | 437200    | 0.13            |

| Slice LUT       | 412      | 218600    | 0.19            |

| DSP             | 3        | 900       | 0.33            |

Display the resource utilization for the transpose delayed LMS filter in HDLDelayedLMSModel.slx model.

```

F = table( ...

categorical({'Slice Registers'; 'Slice LUT';'DSP'}), ...

categorical({'3395'; '2914'; '33'}), ...

categorical({'437200'; '218600'; '900'}), ...

categorical({'0.78'; '1.33'; '3.67'}), ...

'VariableNames',{'Resources','Utilized','Available','Utilization (%)'});

disp(F)

```

| Resources       | Utilized | Available | Utilization (%) |

|-----------------|----------|-----------|-----------------|

|                 |          |           |                 |

| Slice Registers | 3395     | 437200    | 0.78            |

| Slice LUT       | 2914     | 218600    | 1.33            |

| DSP             | 33       | 900       | 3.67            |

#### References

[1] Hayes, M.H. Statistical Digital Signal Processing and Modeling. New York: John Wiley & Sons, 1996.

#### See Also

#### **Blocks**

LMS Filter

#### **Objects**

dsphdl.LMSFilter|dsp.LMSFilter

# **High Performance DC Blocker for FPGA**

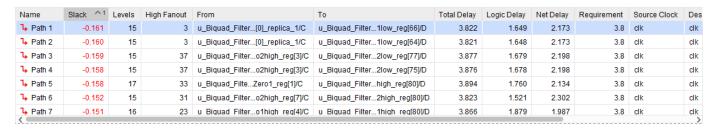

This example shows how to create a DC blocking filter for a communications system by using the Biquad Filter block in DSP HDL Toolbox $^{\text{\tiny TM}}$ .

A DC blocking filter is used in many communications system designs to simplify other filtering requirements. A DC blocking filter is a overall high-pass filter with a very low frequency transition frequency that typically achieves the highpass response by subtracting a lowpass version of the input from the input, leaving just the portions of the signal above DC.

This application is a natural fit for infinite impulse-response (IIR) filters since they are able to provide a steep transition bandwidth with fewer resources than a more common finite impulse response (FIR) filter. A drawback of an IIR filter is that stability of the filter is not guaranteed, so generally a second-order section (SOS), also known as a biquad filter, design is used. Biquad filters can guarantee stability even after fixed-point quantization.

This example shows three implementations of a DC blocker algorithm for hardware. The Biquad Filter block in DSP HDL Toolbox provides options to select different SOS filter architectures to achieve different tradeoffs of resources and throughput in your design.

#### **Reference DC Blocker Block**

The Communications Toolbox $^{\text{TM}}$  DC Blocker Simulink block can provide a behavioral reference for your hardware design. It supports four types of filters: IIR, FIR, cascaded integrator comb, and subtract mean. This example focuses on IIR filters. The block is designed for floating-point operation and has two parameters for an IIR DC blocking filter: the normalized bandwidth of the lowpass stopband and the order of the filter. The block automatically designs an SOS or biquad filter from these parameters with a passband ripple of 0.1 dB and a stopband attenuation of 60 dB.

The block uses an elliptical filter design method, which provides steeper roll-off transition bandwidth characteristics than Butterworth or Chebyshev filter designs and often allows the lowest order for a given frequency response. The downside to this type of filter is that the poles and zeros are often very close to the unit circle and the stability of a quantized filter can sometimes be challenging.

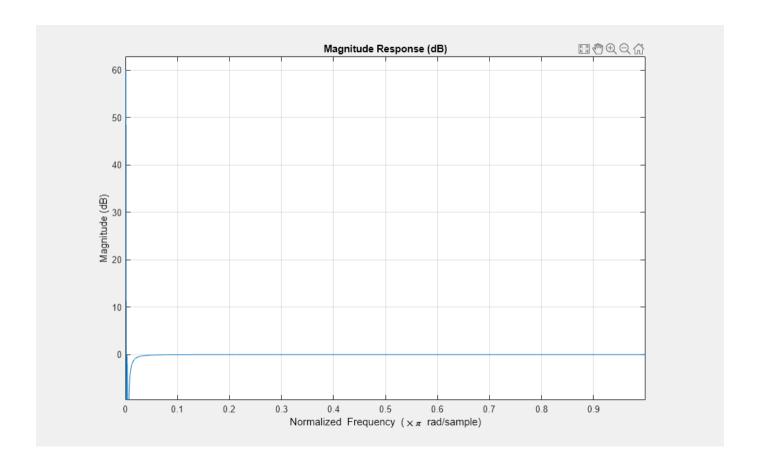

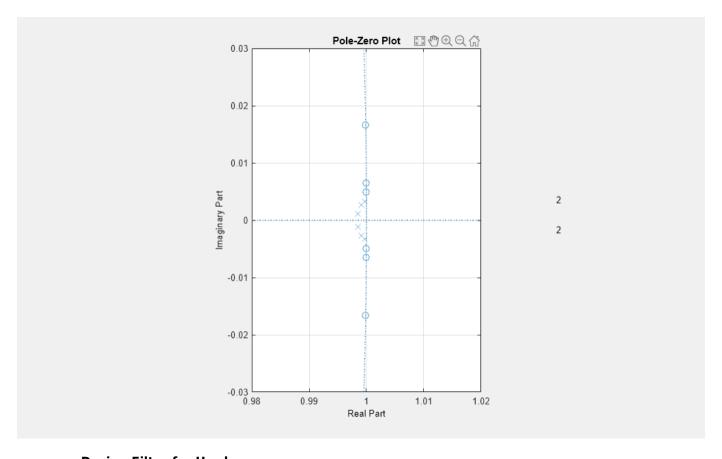

When you design SOS or biquad filters, use a design method that returns zeros, poles, and gain, (z,p,k), rather than the multiplied-out transfer function, (b,a), since the transfer function polynomial can have numerical instability. The DC Blocker block returns zeros, poles, and gain similar to this filter design code. The poles in the pole-zero plot (represented by x values) are very near but still inside the unit circle, making the double-precision filter stable.

#### **Design Filter for Hardware**

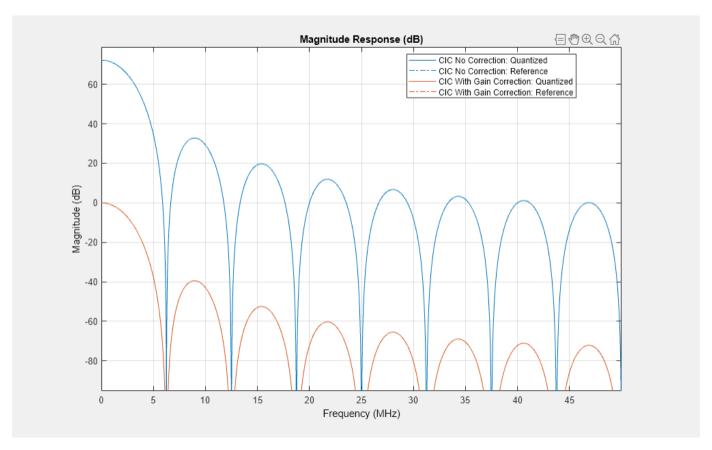

Quantizing the numerator and denominator coefficient independently allows for better results, so this code separates the numerator and denominator before quantization. This design has 12-bit input and targets a typical DSP element in an FPGA, so the example uses 20-bits for numerator and denominator coefficients. The pole-zero plot shows the quantized fixed-point numerator and denominator coefficients after they are converted back to double data type for analysis. You can confirm that the quantized filter is stable by changing the Analysis setting in the Filter Visualization Tool to Filter Info.

```

numerator = sos(:,1:3);

denominator = sos(:,4:6);

scaleValues = g;

scaledDoubleSOS = [double(fi(numerator,1,20)),double(fi(denominator,1,20))];

f3 = fvtool(scaledDoubleSOS,'polezero');

zoom(f3,[0.98 1.02 -0.03 0.03]);

```

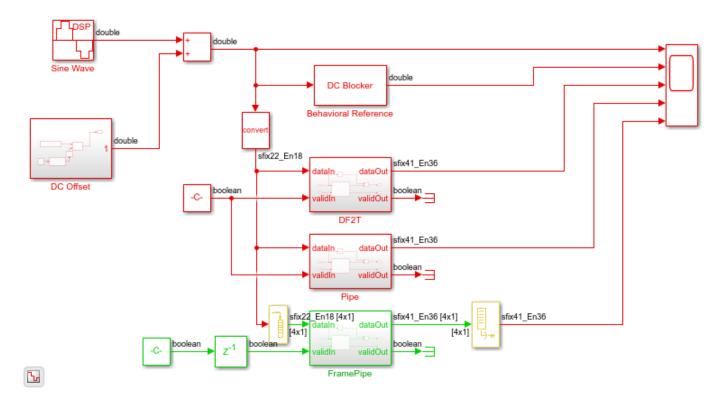

The example model shows three different modes of the Biquad Filter block as well as the original behavioral model of the DC Blocker from the Communications Toolbox library.

```

modelname = 'DCBlockerHDL';

open_system(modelname);

set_param(modelname, 'SampleTimeColors', 'on');

set_param(modelname, 'SimulationCommand', 'Update');

set_param(modelname, 'Open', 'on');

set(allchild(0), 'Visible', 'off');

```

The DF2T subsystem contains a Biquad Filter block with the **Filter structure** parameter set to Direct form II transposed.

The Pipe subsystem contains a Biquad Filter block with the **Filter structure** parameter set to Pipelined feedback form.

The FramePipe subsystem also contains a Biquad Filter block with the **Filter structure** parameter set to Pipelined feedback form. This subsystem uses 4-sample vector input to parallelize the filter operation and increase throughput.

In each of the subsystems, the result of the Biquad Filter is subtracted from the input data delayed to match the latency of the filter. All of the subsystems compute the same results, but each filter uses different hardware resources and synthesizes to a different clock rate. The rest of this example compares the resources, clock rate, and throughput of each of the biquad filter structures.

#### **Direct Form II Transposed Filter Structure**

To create a unique folder for the generated HDL code for each filter implementation, add the TargetDirectory name-value argument to the makehdl function call. Use this command to generate HDL code for the direct-form transposed filter.

```

makehdl('DCBlockerHDL/DF2T','TargetDirectory','df2t');

```

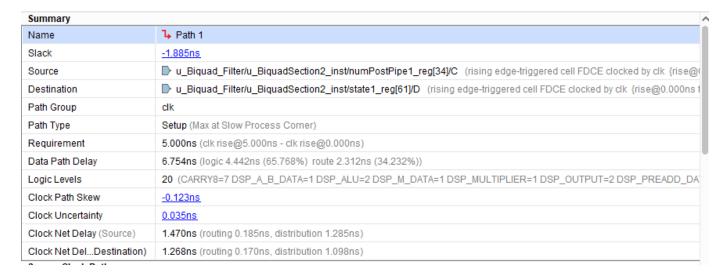

This figure shows the Xilinx® Vivado® synthesis results for the DF2T filter implementation. The synthesis tool was run with a 5 ns clock period to target 200 MHz operation, but the post-synthesis timing report shows that the minimum achievable clock period is only 6.754 ns or around 148 MHz. The critical path in this filter implementation goes through a DSP block, which is efficient use of hardware resources, but does not meet the 5 ns target.

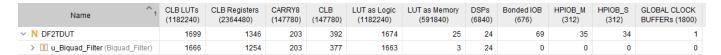

The resource utilization for this filter structure, which has three second-order sections and one gain value, is 24 DSP elements, with 6 in the denominator and 18 in the numerator. The synthesis tool implemented the gain using shift-and-add logic.

#### Pipelined Feedback Filter Structure for Higher Clock Rate

The pipelined structure creates a new denominator that has higher powers in Z (that is, more delay). This new denominator introduces more poles in the filter but these poles are canceled by a modified numerator. The new poles are created from the roots of the original denominator raised to a power determined by the amount of pipelining required. Since the poles are less than one for a stable filter, the new poles are smaller than the starting values, which adds to filter stability. This structure usually results in higher synthesis clock rates because of the additional pipelining. Use this command to generate HDL code for the pipelined feedback filter.

```

makehdl('DCBlockerHDL/Pipe','TargetDir','pipe');

```

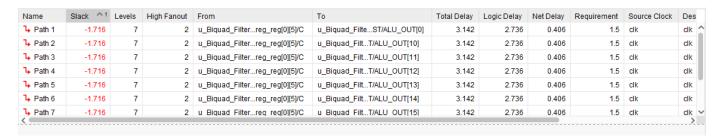

The post-synthesis timing report shows that the design has a minimum clock period of 3.142 ns or around 318 MHz, which is more than twice the speed of the DF2T version. Since this filter processes one sample per clock, this rate corresponds to 318 megasamples/s.

The resource utilization for this filter structure uses 84 DSP elements. There are 6 DSPs in the denominator and 18 DSPs in the numerator as before, and the new numerators (one per section) that cancel the added poles in the denominator use 60 DSP elements in total.

#### Pipelined Filter with Frame Input for Highest Clock Rate

This filter implementation increases throughput by using the frame input and output mode. This mode goes by many names including frame-based, vector, and super-sample-rate (SSR). All of these names mean that the algorithm processes more than one sample per clock cycle. You can use the buffer block in Simulink to switch between input sizes and try different designs. The model in this example is configured for four samples per clock. Use this command to generate HDL code for the pipelined feedback filter with frame-based input.

```

makehdl('DCBlockerHDL/FramePipe','TargetDir','framepipe');

```

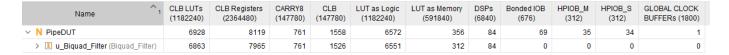

The post-synthesis timing report shows that the achievable clock rate for the four-sample-per-clock implementation is around 275 MHz.

The critical path for this implementation is in the pipelined addition of the modified numerator, which has large word lengths due to the fixed-point requirements of this particular filter design.

Even with the lower clock rate, the throughput per clock is four times larger so this design processes about 1.1 gigasample/s.

The resource utilization for this filter structure shows that this filter uses 510 DSP elements and many more CLB elements as well. This increase is because the size of the new numerator added to cancel poles in the expanded denominator scales with the number of samples per cycle.

The pipeline depth for the Biquad Filter block in this mode is 4 pipeline stages per multiply and one pipeline stage for every addition. For a given number of samples per clock, FrameSize, the size of the new numerator is 2\*FrameSize\*4-1. For a frame size of 4, the new numerator has 31 taps.

#### **Going Further**

If you explore filter stability by quantizing the numerator and denominator using 16 bits instead of 20 bits, you can see that the filter becomes unstable. The filter coefficients in this example actually require a minimum word length of 19 bits for a stable filter.

You can try different frame sizes to increase throughput. As the frame size increases, the denominator coefficients get smaller and the filter numerics become more challenging. If the

coefficients are quantized to zero, the Biquad Filter block issues a warning. Sometimes, increasing the word length for the denominator is the only way to avoid numeric problems since the scale of the two internally computed coefficients can differ by more than the word length you select.

At some point, the size of the logic added to handle a larger frame size exceeds the size of an equivalent FIR filter. In this design, you can experiment with the transition bandwidth for an FIR filter, starting from the normalized frequency used to design the IIR filter of 0.001. An FIR filter that matches that frequency specification has over 5000 taps and consumes considerably more resources than the IIR filter in the Biquad Filter block.

#### See Also

#### **Blocks**

Biquad Filter

# Frequency-Domain Filtering in HDL

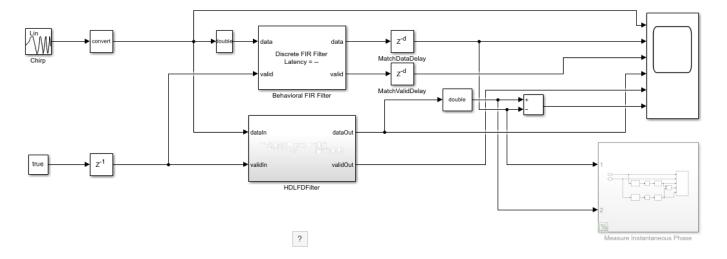

This example shows how to implement a filter in the frequency domain.

A sinusoidal input is filtered with the overlap-add method using a frequency-domain FIR filter built using the DSP HDL Toolbox FFT and IFFT blocks. The overlap-add and overlap-save filtering methods are area efficient ways to compute the discrete convolution of a signal with a finite-impulse response (FIR filter). The efficiency gain is particularly noticeable for high-order filters with a large number of taps. Match filters in communications systems, high-order FIR filters, and channel models on FPGA/ASIC hardware are all good examples of systems where frequency-domain filtering is a good choice.

#### Open and run the model.

The overlap-add algorithm [1] filters the input signal in the frequency domain. The input is divided into non-overlapping blocks which are linearly convolved with the FIR filter coefficients. The linear convolution of each block is computed by multiplying the discrete Fourier transforms (DFTs) of the block and the filter coefficients, and computing the inverse DFT of the product. For filter length M and FFT size N, the last M-1 samples of the linear convolution are added to the first M-1 samples of the next input sequence. The first N-M+1 samples of each summation result are output in sequence.

```

modelname = 'FreqDomainFiltHDL';

open_system(modelname);

set_param(modelname, 'SampleTimeColors', 'on');

set_param(modelname, 'Open', 'on');

set(allchild(0), 'Visible', 'off');

```

Copyright 2022 The MathWorks, Inc.

#### Selecting the FFT Size

In selecting an FFT size for a particular filter, you must take care to make a hardware-friendly choice. If the filter length is an exact power of two, then your FFT size must be exactly double your filter length. In this case with a power of two size, there will be no time, except for the first filter length of

samples, where you will not be adding overlapping results. This simplifies the timing of the design since only the starting period must be handled specially.

If your filter length is not an exact power of two, then you must choose an FFT size that is larger than the next power of two from the filter length. In this example, the filter has 300 coefficients, then the next power of two would be 512, but you must choose 1024 for the FFT size. If you try to use the smaller size of 512 and check the timing, you will find that there are three overlapping regions, not two, and the hardware design becomes more complicated and area intensive.

#### Converting to Two-samples at a Time

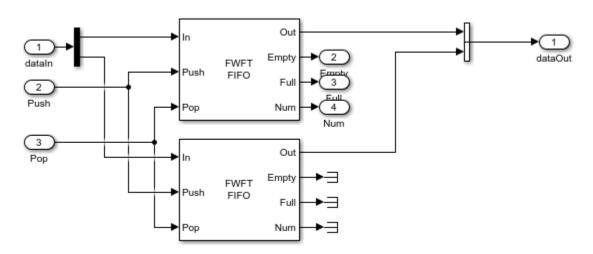

In hardware, computing the FFT of N-(M-1) samples must be done by zero padding the input to the FFT block after the block of samples is sent in. This padding takes time away from processing the input samples, so somehow you must gain the time it takes to pad the input. One way to accomplish this is to buffer sample into a larger frame of say two samples and process these in a frame-based FFT block. Since you also need to buffer samples for a time, a FIFO is a natural buffer to use at the input.

open system([modelname '/HDLFDFilter/In FIF0'], 'force');

#### **Point Multiplication**

The output of the FFT is then multiplied point-by-point, using a pipelined multiplier, with the FFT of the filter coefficients. In this example, the FFT of the filter coefficients is precomputed but for dynamic filter coefficients, but you can add another FFT to compute the coefficient transform. The result of the point multiply is then sent to an IFFT block to be transformed back into the time domain.

open\_system([modelname '/HDLFDFilter'],'force');

#### **Design Considerations**

Another important consideration in making the frequency-domain filter hardware-friendly is that the shift from one sample at a time to two (or other power of 2) samples at a time means that the point at which the design switches from the non-overlapped region to the overlapped region must happen on a boundary that is divisible by two (or the selected power of 2) to avoid difficult timing in the design. You would like to switch between the non-overlapped region and the overlapped region on boundary that lines up with the change to a vector of samples. This adds a condition that your filter length must be divisible by your vector size. Also note that odd-order filters (with an even number of taps) will be required.

In this example, the filter transfer function is designed to be a low-pass filter so using a chirp or swept tone input signal allows you to easily visualize the frequency response of the filter directly in Simulink. You must design this filter with a larger than default Density Factor in order for the filter design to converge to a solution. The designed filter has 300 taps and is fully symmetric and so would require 150 multipliers to implement in the conventional way. By using a frequency-domain filtering approach, you are able to reduce this considerably. Care should be taken when comparing multiplier counts since the FIR implementation uses real-only multipliers but the FFT, point-multiply, and IFFT use complex multipliers and therefore require 3 or 4 real multipliers depending on the architecture selected.

#### **Exploring the Filter Response**

You can explore the filter response by looking at the transformed, then quantized, then inverse transformed coefficients versus the original coefficients.

Num is the filter coefficients you calculated and FFTNum is the transform of those coefficients in double precision. You can simulate what the frequency response of the frequency-domain filter will be by quantizing FFTNum and then translating that back into the time domain.

The quantized transformed filter coefficients for the frequency-domain filter require different quantization settings since they can range between above 1 and below -1. Use the fixed-point tools to find the best precision binary point for the data by supplying only the signedness and the word length. Using fvtool for analysis allows you to overlay the data for both the original and the transformed filter coefficients.

```

QNum = fi(Num,1,18);

QFDNum = ifft(double(fi(FFTNum,1,18)));

QFDNum = QFDNum(1:300);

h = fvtool(double(QNum),1,double(QFDNum),1);

set(h,'OverlayedAnalysis','phase');

```

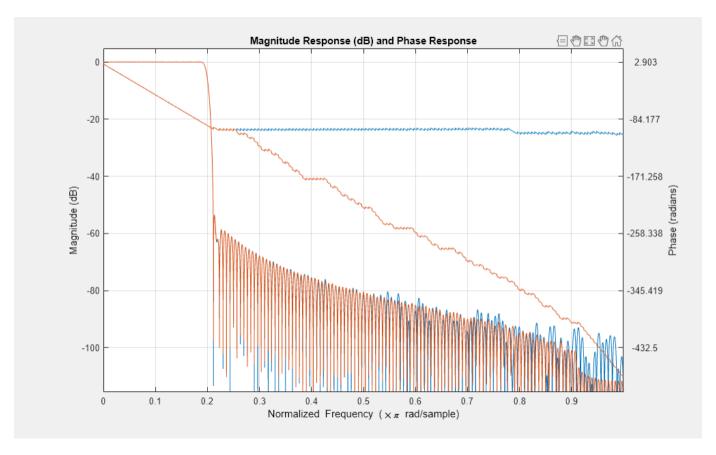

As you can see in fvtool, the magnitude responses of the two filters match very closely with some minor variations in the stopband up until frequencies very near Nyquist. The phase response matches very closely in the passband but varies significantly in the stopband. The original filter shows some ripples but nearly constant phase in the stopband while the frequency-domain filter shows a quantized phase response that falls away rapidly. The phase response of the stopband is not normally an factor in filter design, but it is good to know that the frequency-domain filter does not match the original here.

#### Going further

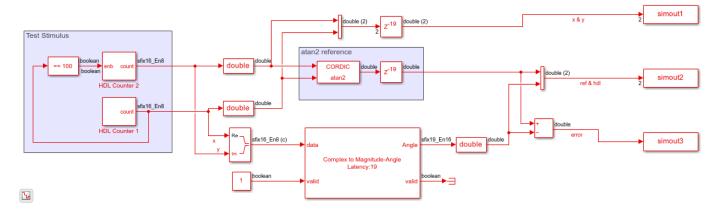

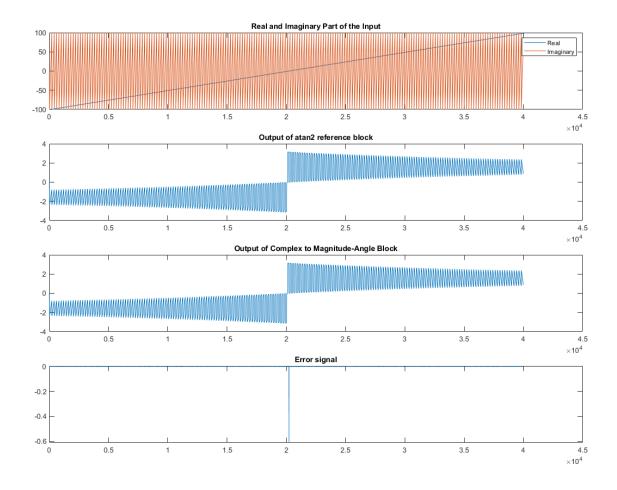

You can also see the change in stopband phase response by computing the instantaneous phase for each both the behavioral FIR and the frequency-domain filter. To do this you can uncomment the subsystem Measure Instantaneous Phase and re-run the simulation. The instantaneous phase of the real outputs is computed using Analytic Signal block followed by a Complex to Magnitude-Angle and finally an Unwrap block to make the phase continuous.

The DSP System Toolbox block Frequency-Domain FIR Filter has an option to partition the numerator to reduce latency. Using this option, the filter performs overlap-save or overlap-add on each partition, and combines the partial results to form the overall output. The latency is now reduced to the partition length. Using this technique on an HDL frequency-domain filter is also possible but you will likely use more multipliers depending on the size of your filter.

The transformed filter coefficients are computed from the FFT of a real sequence. This produces conjugate symmetric output so the upper bins of the FFT are the same values as the lower bins but reversed and with the sign of the imaginary part changed. This conjugate symmetry could allow you

to save half of the storage in the ROM used to store the transformed coefficients since you can map the upper bins to the lower bins in reverse order and conjugate the result. Note that the first bin representing the DC value of the sequence is not used in the reverse upper bins.

You can compare the synthesis results from an FIR filter with the results from the frequency-domain filter. These results can be hard to predict since they depend on the quantization settings used and since the FFT, point-multiply, and IFFT all operated on complex data, each multiplier is either 3 or 4 real multipliers depending on the block settings. Finding the area cross-over point between the two implementations is challenging to predict as well. In this implementation, you used two words at time in order gain the time needed for the overlap regions and allow continuous input, but if your application does not require continuous input, a lower area implementation is possible.

#### References

- [1] Overlap-Add Algorithm: Proakis and Manolakis, Digital Signal Processing, 3rd ed, Prentice-Hall, Englewood Cliffs, NJ, 1996, pp. 430 433.

- [2] Overlap-Save Algorithm: Oppenheim and Schafer, Discrete-Time Signal Processing, Prentice-Hall, Englewood Cliffs, NJ, 1989, pp. 558 560.

# **HDL Implementation of Four Channel Synthesizer and Channelizer**

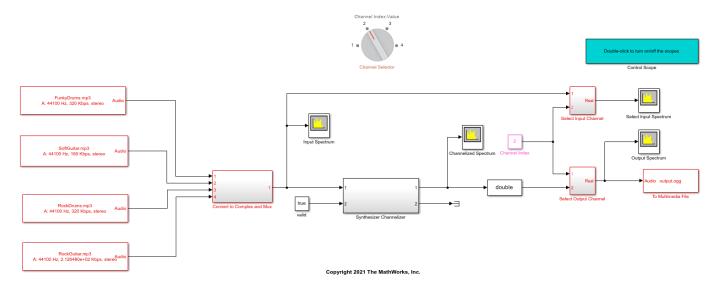

This example shows how to synthesize a series of four stereo signals into a broadband signal using a channel synthesizer and how to split the synthesized broadband signal into four individual narrowband signals using a channelizer. The Simulink® model in this example contains a Synthesizer Channelizer subsystem with Channel Synthesizer and Channelizer blocks. These blocks support HDL code generation.

#### **Data Source**

Use these stereo signals as model inputs.

- FunkyDrums.mp3

- SoftGuitar.mp3

- RockDrums.mp3

- RockGuitar.mp3

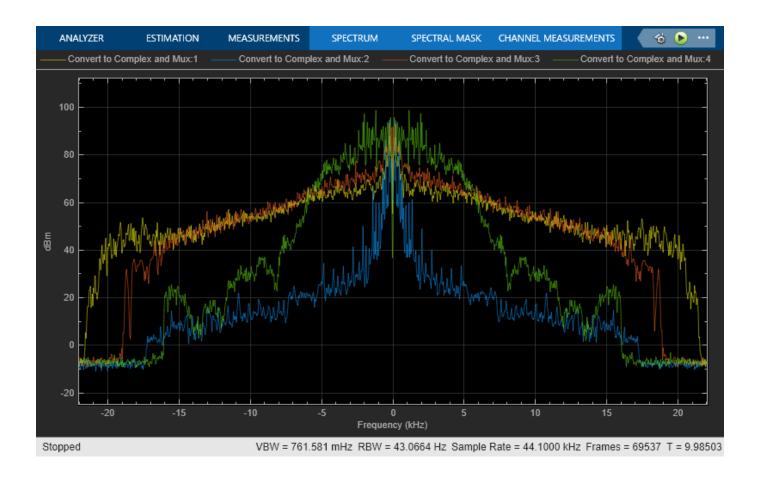

Each stereo signal has two samples. The two channels in the model represent the left and right channels of a stereo signal. To store the channels of a stereo signal, convert each signal into a complex signal, multiplex, and then transpose to form a 1-by-2 vector.

#### **Model Structure**

Open the model.

```

model = 'HDLSynthesizerChannelizer';

open_system(model);

```

#### **Model Parameters**

The InitFcn callback sets up the model. To access the InitFcn callback, right-click the model, click **Model Properties**, open the **Callbacks** tab, and then click InitFcn. In the Channelizer block, set

the **Number of frequency bands** parameter to 4. Each band has one FIR filter and each FIR filter has 24 taps, so the model has total of 96 filter taps. The designMultirateFIR function designs a multirate FIR filter and generates the filter coefficients. Set the number of taps per band and stopband attenuation. Calculate the filter coefficients by using the designMultiRateFIR function.

```

M = 4; % number of frequency bands

P = 24; % number of taps per band

Astop = 120; % stop band attenuation

b = designMultirateFIR(1,M,ceil(P/2),Astop); % filter coefficients

```

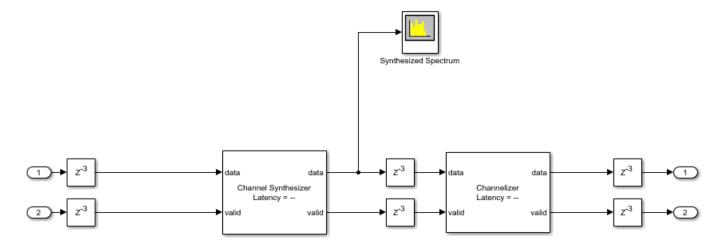

#### Synthesizer and Channelizer

The Channel Synthesizer block synthesizes the input signals into a single broadband signal of size 4-by-1 by using an FFT-based synthesis filter bank. The model passes this signal to the Channelizer block. The Channelizer block splits the broadband input signal into four narrowband output signals. The output of the Channelizer block is a 1-by-4 vector, where each channel represents a narrowband.

Open the Synthesizer Channelizer subsystem.

```

open system([model '/Synthesizer Channelizer']);

```

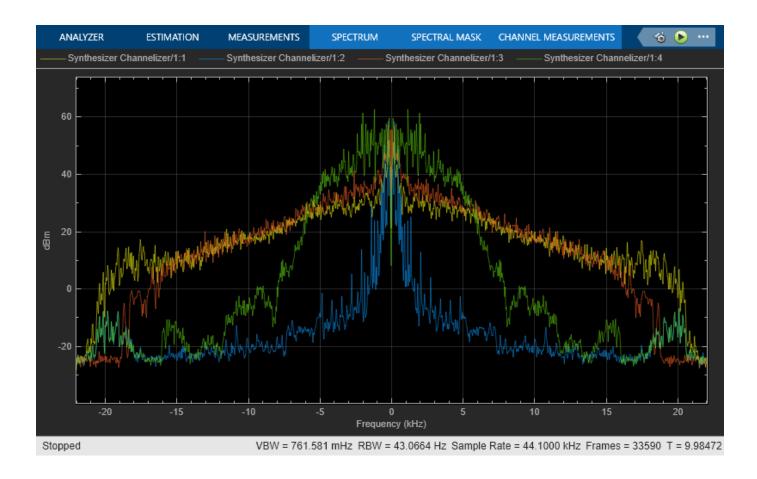

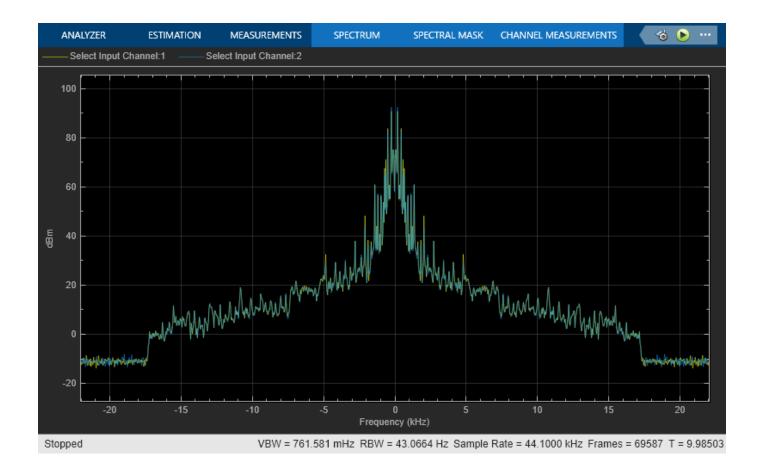

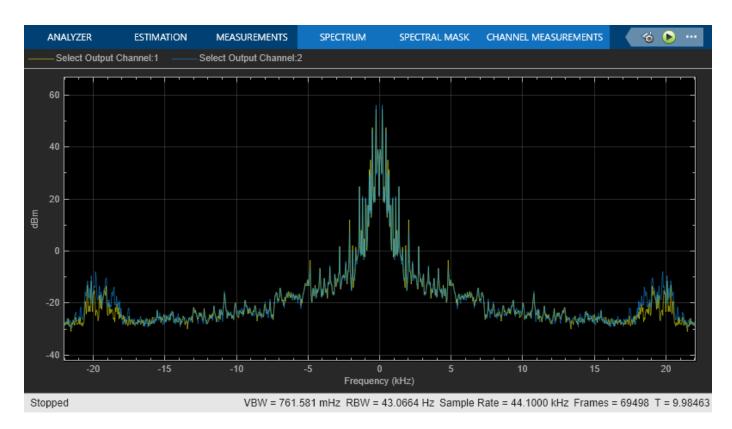

View the spectra of the input, synthesized signal, channelized signal, and synthesized-channelized output signal. The **Synthesized Spectrum** window shows the spectrum of the broadband signal. The **Channelized Spectrum** window shows the spectra of the four narrowband signals. The input and output spectra match for any selected signal.

```

open_system([model '/Control Scope']);

sim(model)

```

1-37

1-39

#### **Audio Capture**

Collect the output samples and reproduce the audio.

```

% Create a |dsp.AudioFileReader| object with default settings.

fileReader = dsp.AudioFileReader('output.ogg');

% Return a structure containing information about the audio file.

fileInfo = audioinfo('output.ogg');

% Create an |audioDeviceWriter| object and specify the sample rate.

deviceWriter = audioDeviceWriter('SampleRate',fileInfo.SampleRate);

% Reduce the computational load of initialization in the audio stream loop.

setup(deviceWriter,zeros(fileReader.SamplesPerFrame,fileInfo.NumChannels));

% In the audio stream loop, read the audio signal frame from the file and

% write the frame to your device.

while ~isDone(fileReader)

audioData = fileReader();

deviceWriter(audioData);

end

% Close the input file and release the device.

release(fileReader);

release(deviceWriter);

% Save and close the model.

open_system([model '/Control Scope']);

close_system(model,0)

```

#### **HDL Code Generation and FPGA Implementation**

To generate the HDL code for this example, you must have the HDL Coder™ product. Generate HDL code and an HDL testbench for the Synthesizer Channelizer subsystem. Synthesize this subsystem on a Xilinx® Zynq®-7000 ZC706 evaluation board. The table shows the post-place-and-route resource utilization results. The design meets the timing requirement with a clock frequency of 191.4 MHz. The resources and frequencies vary with the parameter values that you select in the block mask.

#### See Also

Channelizer | Channel Synthesizer

### Related Examples

• "High-Throughput Channelizer for FPGA"

## **Gigasamples-per-Second Correlator and Peak Detector**

This example shows how to implement a high-throughput frame-based correlator and peak detector. The system is suitable for applications such as lidar and mm-wave radar.

Lidar and radar systems operate by transmitting pulses, receiving the sent pulse in a stream of data, and using signal processing techniques to determine where in the receiver stream the pulse is located. When you design such a system, one of the main considerations is the pulse width or pulse duration. Pulse width is a measure (in seconds) of how long each pulse transmission is. Longer pulses have more energy and can therefore increase the range of the system. Shorter pulses cannot travel as far, but they can achieve greater accuracy in resolving the distance between objects. The pulse width determines the signal bandwidth. For example, a pulse width of 2 ns results in a signal bandwidth of 500 MS/s. The signal bandwidth is then used to determine the minimum distance where separate objects can be resolved from one another. This distance is the *range ambiguity* and is equal to c/(2\*B), where c is the speed of light, and b is the signal bandwidth.

In high-precision lidar systems, the pulse width can often be as short as 4 ns. This width corresponds to a signal bandwidth of 250 MS/s and range ambiguity of 0.6 m. This calculation does not assume any additional signal processing, such as pulse compression, which could improve the accuracy. To meet the Nyquist rate, the received signal must be sampled at a rate of at least 500 MS/s. In practice, systems often oversample to improve performance. Typically, FPGAs run at up to 500 MHz. To process data with sample rates greater than the maximum clock rate, designs use frame-based processing, where each block operates on a vector of input data every clock cycle. In this way, the processing is parallel and sample rate is higher without an increase in clock rate.

This example describes a correlation and peak detection system that uses a 250 MHz clock and an input frame of 16 samples. These parameters enable the system to process a 4 GS/s input stream oversampled by a factor of 16.

#### **Waveform Generation and Matched Filter Design**

Broadly, lidar and radar systems can be split into pulsed waveform systems and continuous waveform systems. Pulsed waveform systems transmit bursts of data and then wait for a period, whereas continuous waveform systems are always transmitting. In each kind of system, you can apply different kinds of modulation to the waveform to enhance different properties such as range and resolution. This example shows a pulsed laser lidar system without signal modulation.

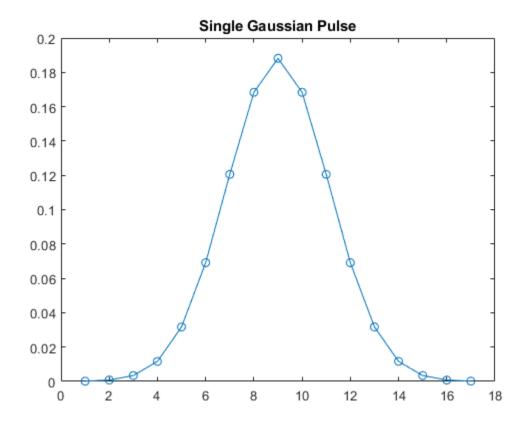

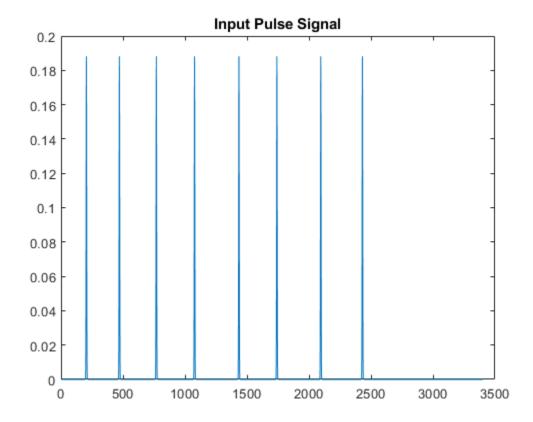

An ideal pulse has a rectangular shape in the time domain, corresponding to a sinc function in the frequency domain. The physical properties of laser systems mean that there is a ramp-up period to peak output, followed by a ramp-down period. Model this input by using a Gaussian function, then generate a stream of zeros and place pulses in the stream.

```

bt = 1; % 3 dB bandwidth-symbol time

sps = 16; % 16 times oversampled

span = 1; % 1 symbol

pulse = gaussdesign(bt,span,sps); % Pulse shape

plot(pulse,'o-');

title('Single Gaussian Pulse')

```

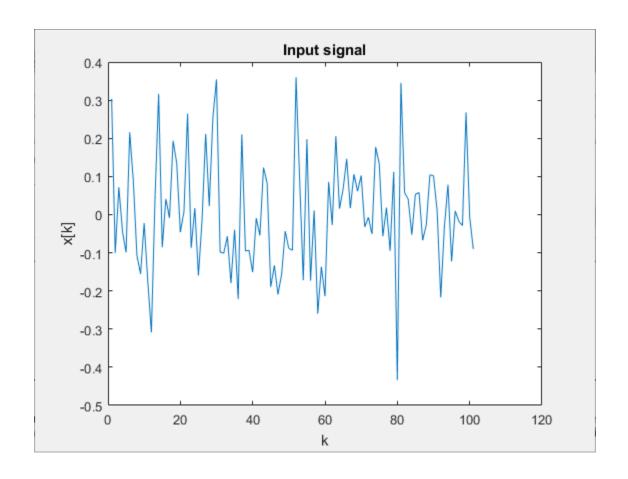

Now, add noise to simulate the channel and design a matched filter, which is the time-reversed conjugate of the pulse. Measure the noise inserted to make sure the calculation was correct. The pulse is symmetric and equivalent to the matched filter.

```

snr = 3;

pulseStream = awgn(tx,snr,10*log10(cov(pulse)),1); % Add in AWGN.

figure

plot(pulseStream);

title('Input Pulse Signal with Noise')

noise = pulseStream - tx;

fprintf('Computed SNR is %3.2f \n',10*log10(cov(pulse)/cov(noise)));

h = flipud(conj(pulse));

isequal(h,pulse)

Computed SNR is 3.02

ans =

logical

1

```

#### **Simulink Design**

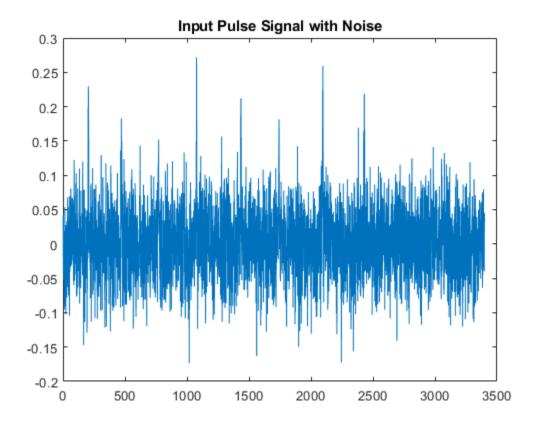

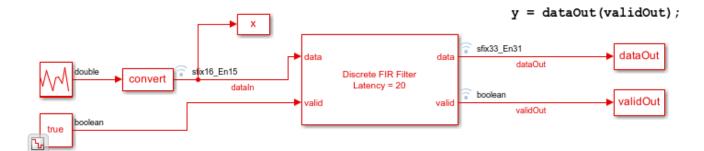

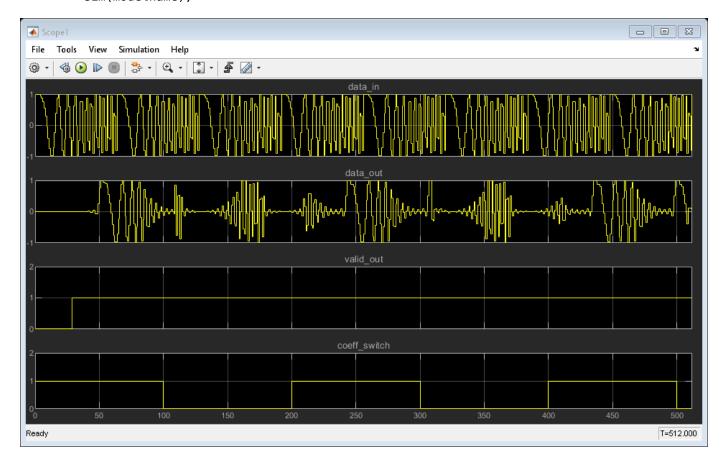

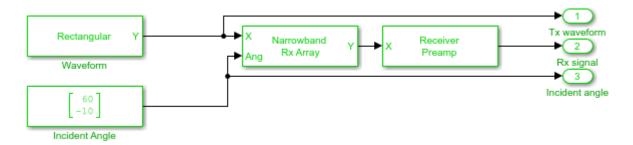

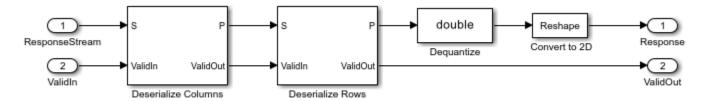

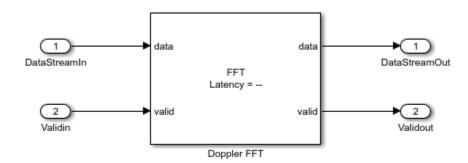

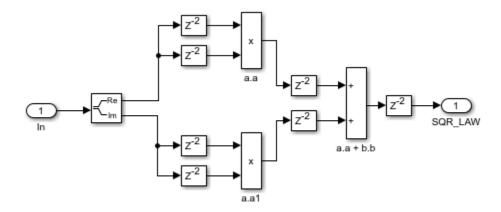

The example model implements a frame-based correlator and peak detector, using the input waveform and filter coefficients from the previous section. The CorrelatorPeakDetector subsystem has three outputs. The magnitude-squared matched filter output shows the boost in the signal-to-noise ratio (SNR) from the correlator. The detected output is a stream of Boolean values, which indicates when a pulse is detected. The valid output indicates when the output data is available.

Ъ

Copyright 2022 The MathWorks, Inc.

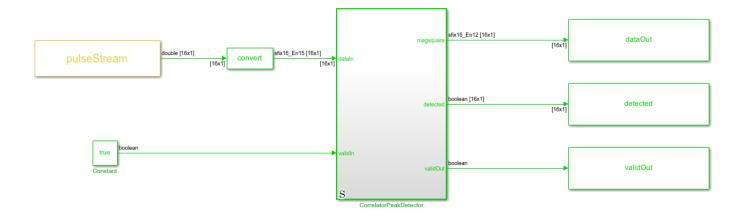

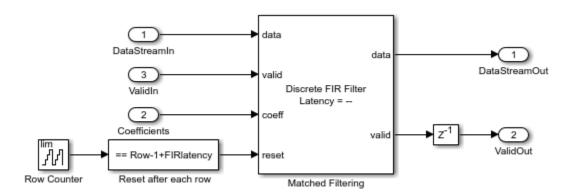

The DUT consists of a correlator or matched filter implemented using a Discrete FIR Filter block and a PeakDetector subsystem. The Discrete FIR Filter convolutes the input stream with the matched filter coefficients and passes the result to the PeakDetector subsystem. The PeakDetector uses a windowing method to determine local maxima.

```

model = 'CorrelationandPeakDetection/CorrelatorPeakDetector';

open_system(model)

```

Synchronous

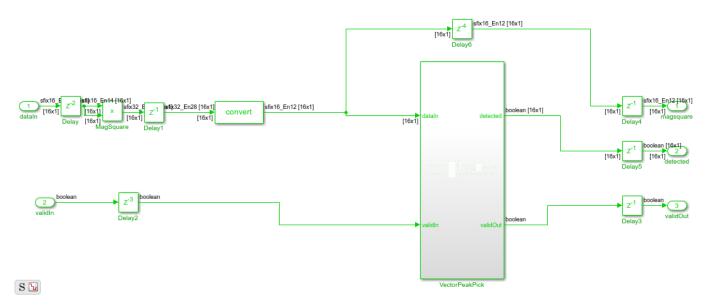

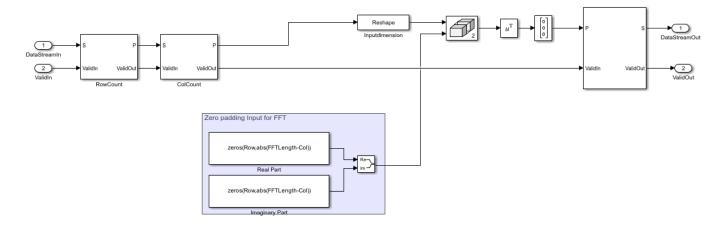

The PeakDetector subsystem forms a sliding window of the FIR results, which is [19x1] for each element of the [16x1] input. An overall vector of [34x1] forms each subwindow. Inside the VectorPeakPick subsystem, the VectorTappedDelay subsystem forms this window and passes it to the subtract\_midpoint subsystem, which implements the peak detection algorithm. The peak detection algorithm assumes that peaks are present when all values in the window subtracted by the middle value are less than or equal to 0. A For Each subsystem repeats this calculation 16 times to check each subwindow.

model = 'CorrelationandPeakDetection/CorrelatorPeakDetector/PeakDetector';

open\_system(model)

#### Verification

Next, run the simulation and verify that the model detects pulses where you expect them, using the information from waveform generation.

```

sim('CorrelationandPeakDetection.slx')

xlocations = find(detected==1); % Find locations where peaks were detected.

prevxlocation = 0; % Check for multiple points for the same peak in the loop below.

addr = 1;

locationsHDL = zeros(length(locations),1);

for ii = 1:1:length(xlocations) % If there are multiple points for the same peak, pick one.

if xlocations(ii) ~= prevxlocation+1

locationsHDL(addr) = xlocations(ii);

addr = addr + 1;

prevxlocation = xlocations(ii);

end

end

latencyHDL = round(mean(locationsHDL - locations')); % Latency is constant, and is the difference

locationsDetected = locationsHDL - latencyHDL

%#ok<NOPTS, NASGU>

locationsDetected =

197

463

761

1069

1427

1733

2087

2422

```

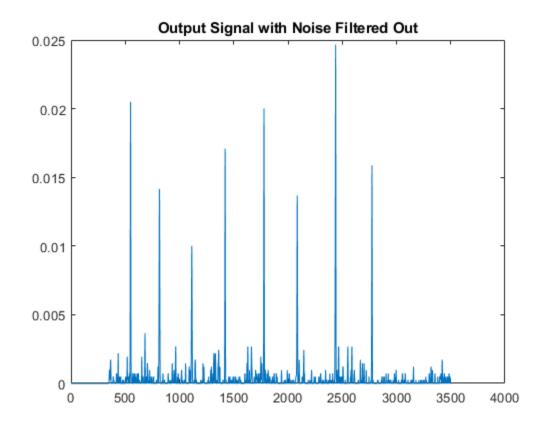

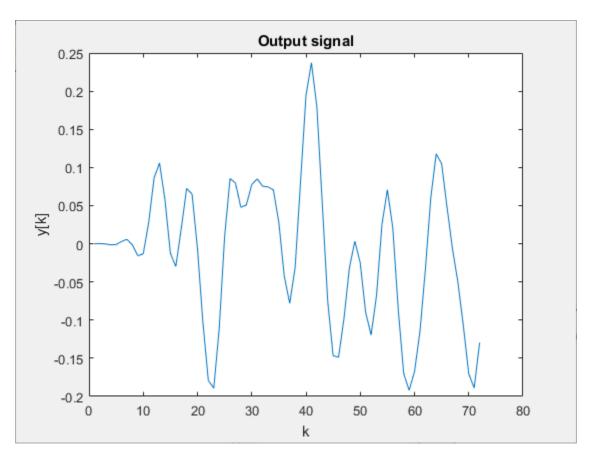

Observe the magnitude squared output to see that the matched filter has significantly boosted the SNR.

```

plot(dataOut);

title('Output Signal with Noise Filtered Out')

```

#### **HDL Implementation Results**

To generate HDL code from this example model, you must have the HDL Coder™ product. HDL was generated for the CorrelatorPeakDetector subsystem and synthesized with Xilinx® Vivado™ targeting a Xilinx Zynq®-7000 SoC ZC706 evaluation board. The design meets timing with a constraint of 400 MHz. The table shows the post place-and-route resource utilization results.

#### Sample Rate Modification Using Scalar Processing

vectorSize = 1; % Scalar processing

You can adapt the model to process input with different sample rates. For example, you can process an input with 25 MS/s oversampled by a factor of 10 and, therefore, with a throughput of 250 MS/s using scalar rather than frame-based input. DSP HDL Toolbox™ library blocks automatically switch between frame and scalar algorithms according to the dimension of the data at the input port. In this example, you can choose to process frame or scalar input by modifying a single parameter, vector\_size. The model automatically determines the correct dimensions for frame or scalar input and processes the data accordingly.

```

sim('CorrelationandPeakDetection.slx') % Run simulation.

xlocations = find(detected==1); % Find locations where peaks are detected.

prevxlocation = 0; % Check for multiple points for the same peak in the loop below.

addr = 1:

locationsHDL = zeros(length(locations),1);

for ii = 1:1:length(xlocations) % If there are multiple points for same peak, pick one.

if xlocations(ii) ~= prevxlocation + 1

locationsHDL(addr) = xlocations(ii);

addr = addr + 1;

prevxlocation = xlocations(ii);

end

end

latencyHDL = round(mean(locationsHDL-locations')); % Latency is constant, and is the difference

locationsDetected = locationsHDL-latencyHDL

%#ok<NOPTS>

locationsDetected =

```

## **NFC Digital Downconverter**

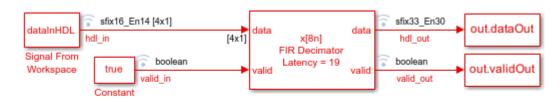

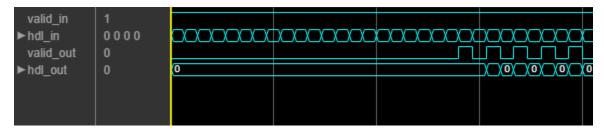

This example shows how to decimate a 100 MS/s ADC signal down to 424 kS/s for a near-field communication (NFC) system.

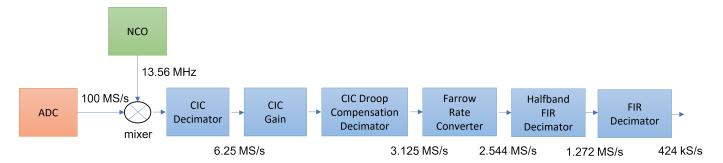

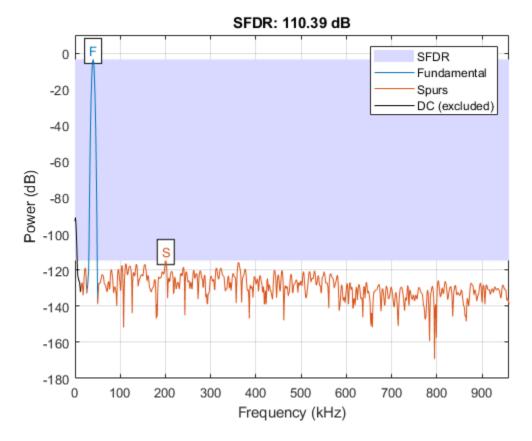

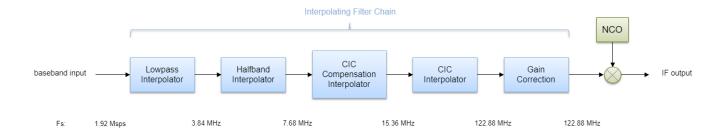

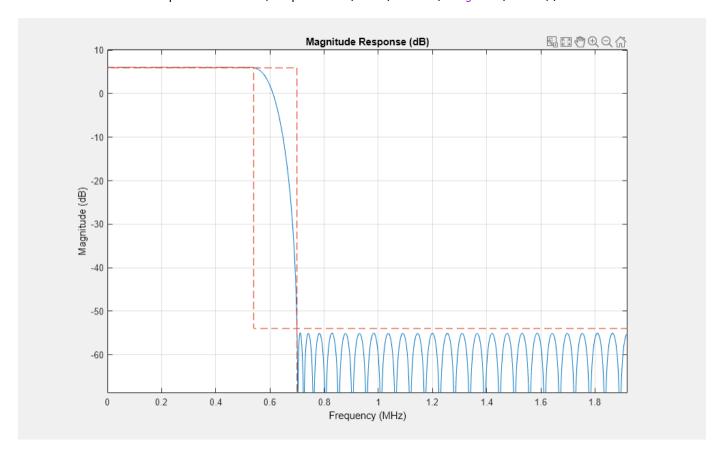

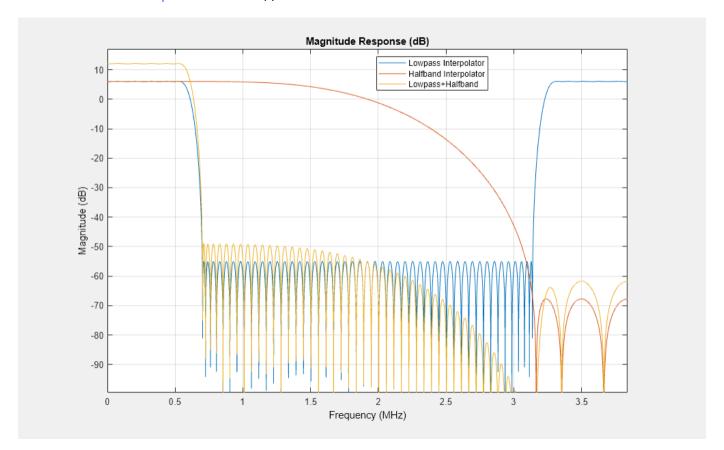

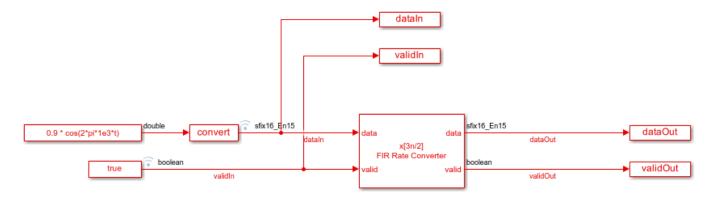

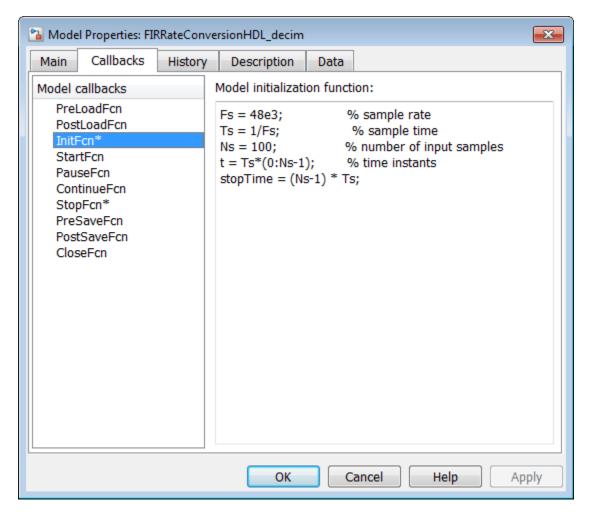

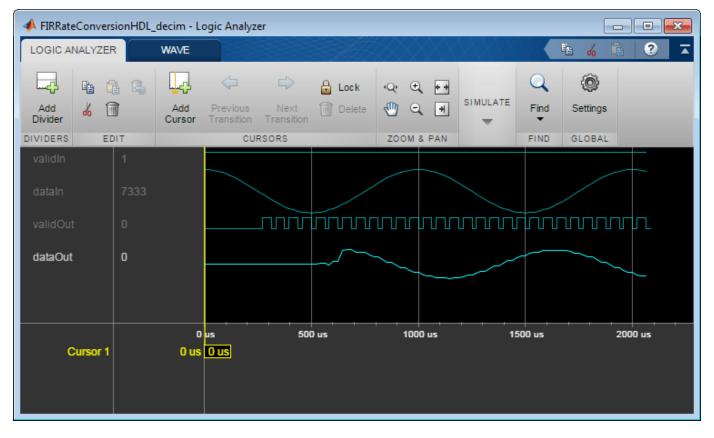

Near-field communication systems operate at data rates of 424, 212, or 106 kS/s. Typical ADCs used in test and measurement (T&M), software-defined radio (SDR), and other prototyping equipment have much higher sample rates in the MS/s range. When you stream data from this equipment to a host computer or processor, the high sample rate can use a lot of memory and processor resources. Lowering the sample rate on the FPGA before streaming data to the host can save host resources. This example includes a digital downconverter (DDC) that converts a 100 MS/s input stream down to 424 kS/s output. The overall rate change is 235.8409566. This example differs from the "Implement Digital Downconverter for FPGA" on page 1-66 example in two ways. First, the decimation factor is much larger in this example, which requires different decimation filters. Second, this example must compute a fractional rate change, rather than a strictly integer rate change.

#### **DDC Structure**

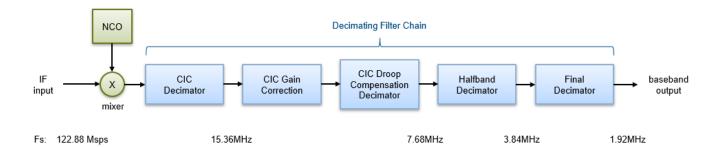

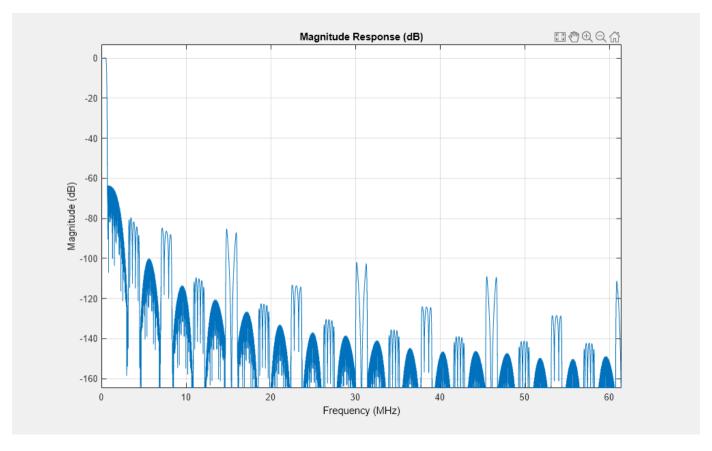

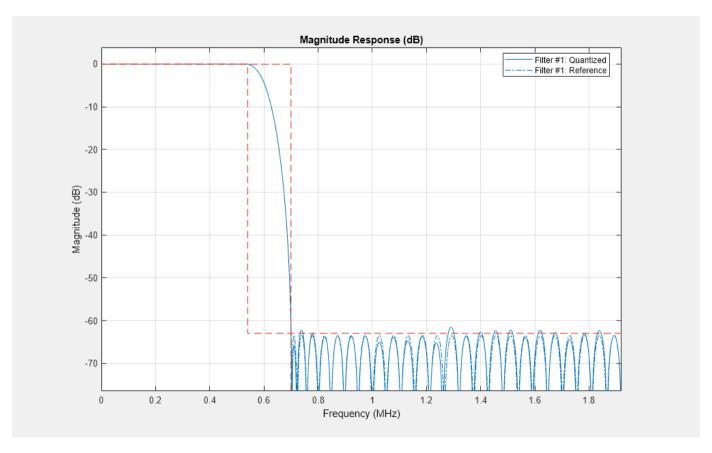

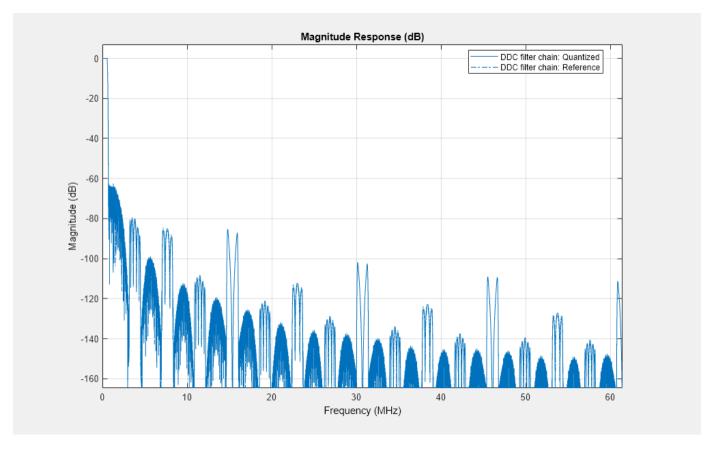

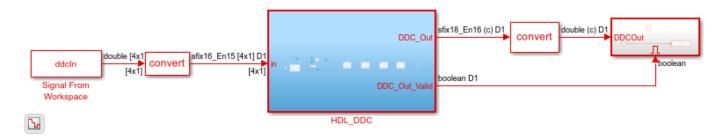

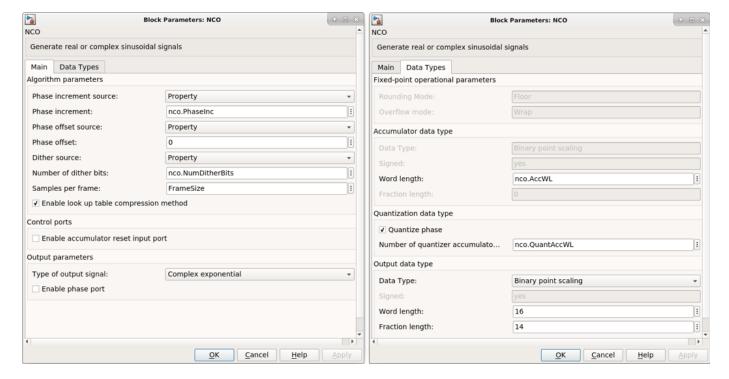

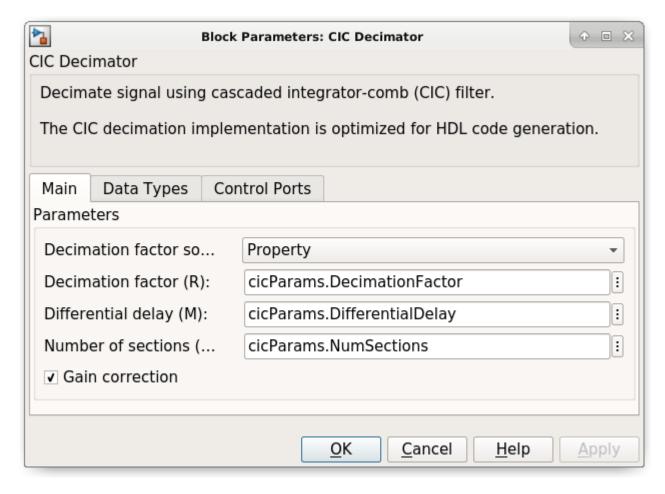

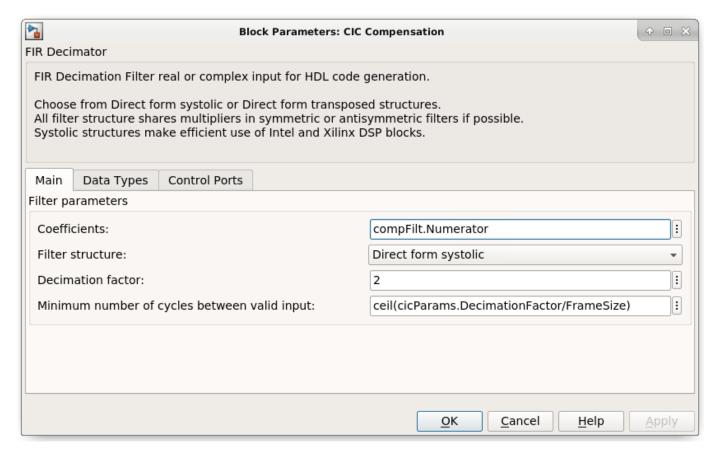

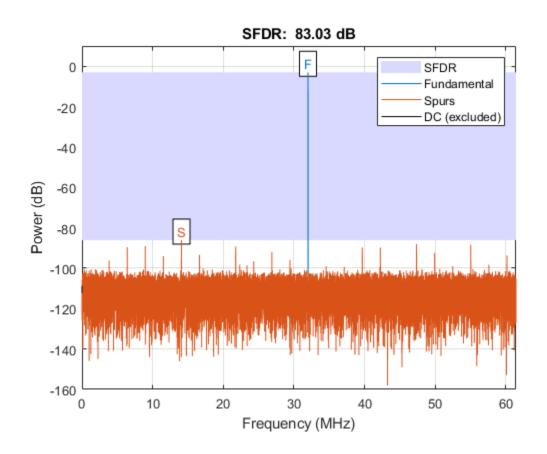

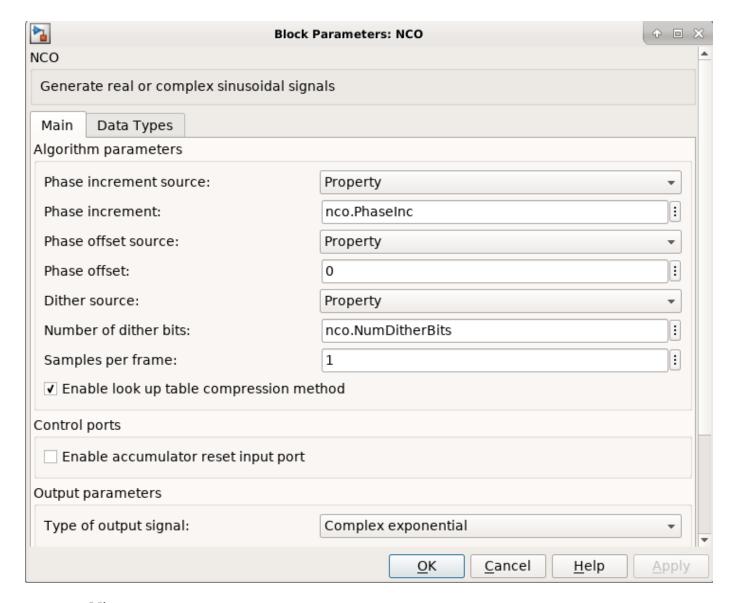

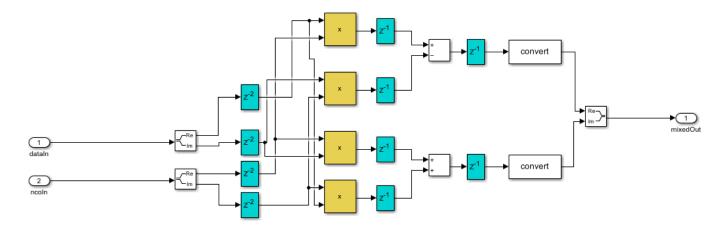

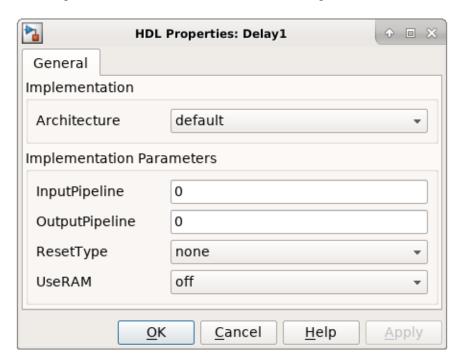

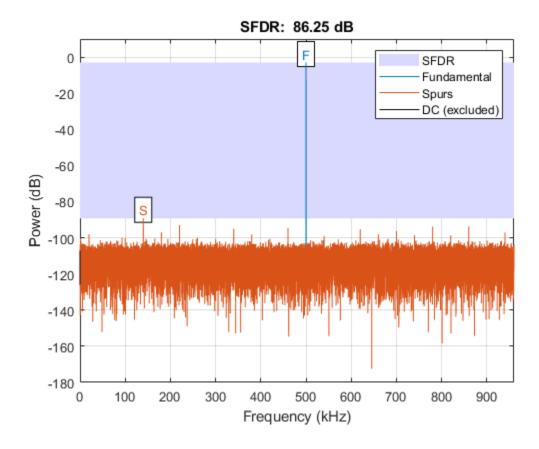

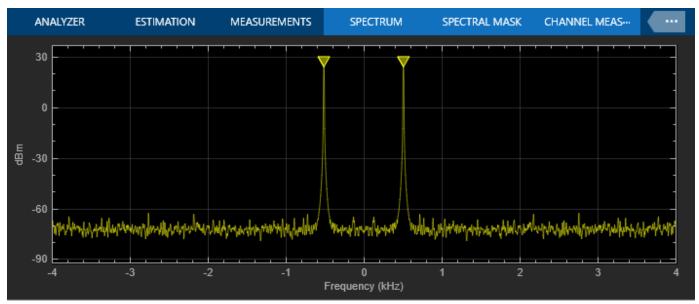

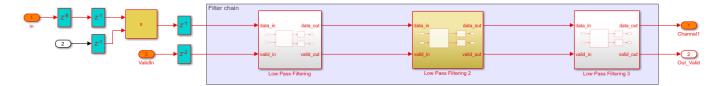

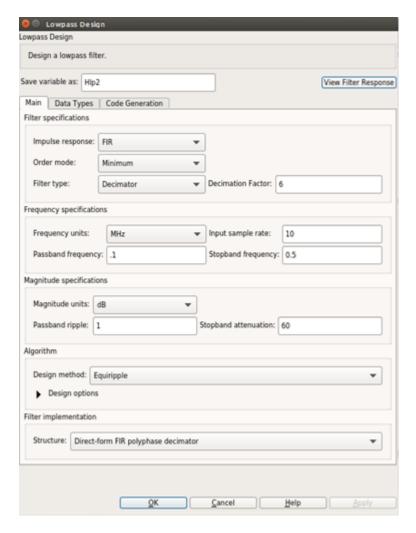

The DDC consists of a numerically controlled oscillator (NCO), mixer, and decimating filter chain. The filter chain consists of a cascade integrator-comb (CIC) decimator, CIC gain correction, CIC compensation decimator (FIR), Farrow rate converter, halfband FIR decimator, and a final FIR decimator.

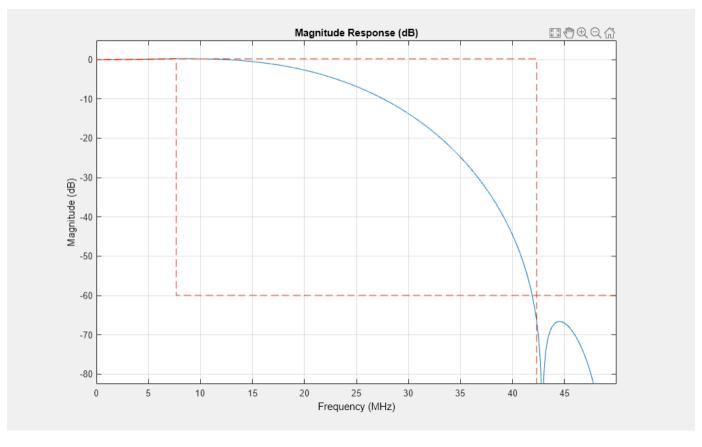

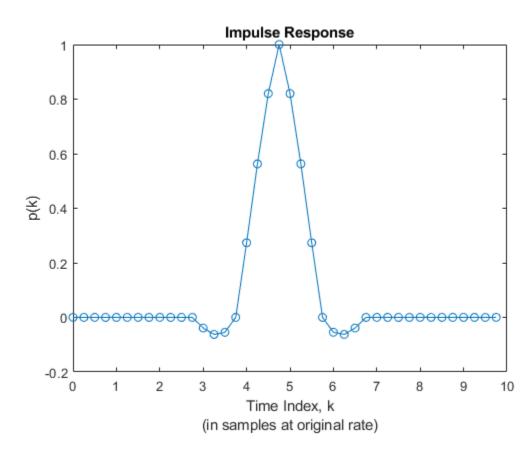

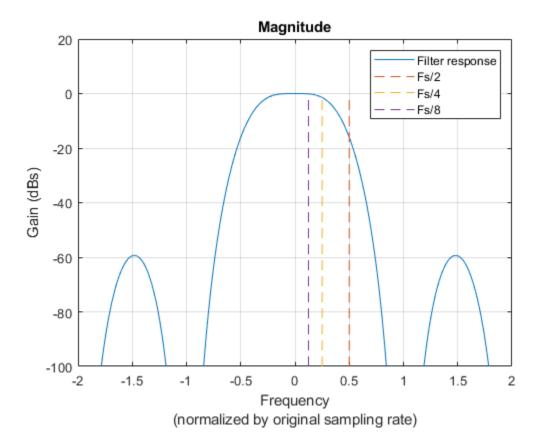

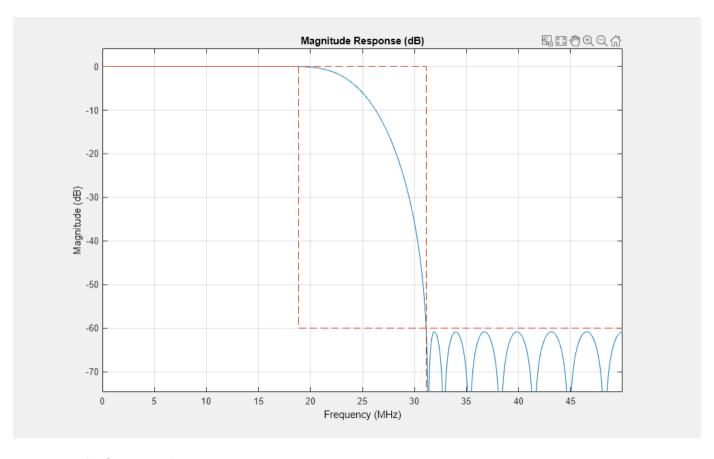

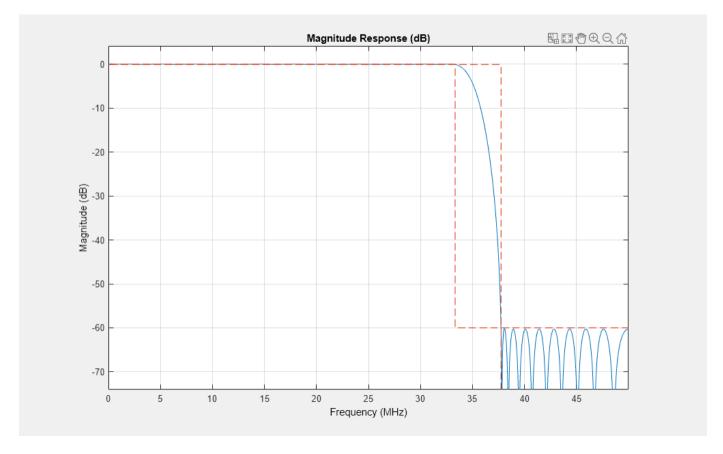

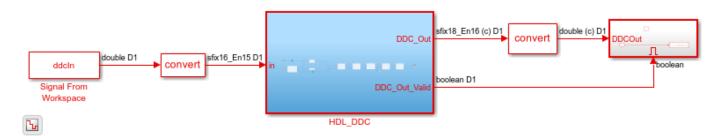

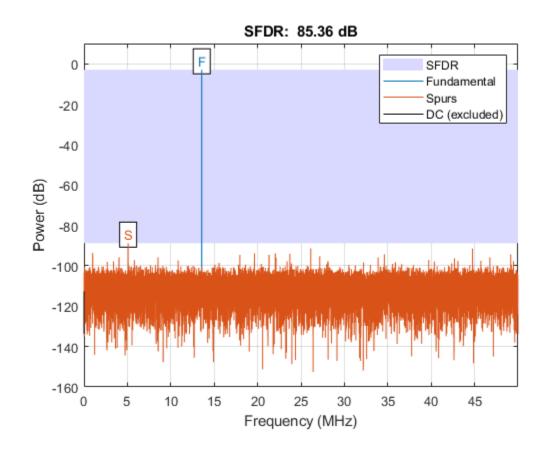

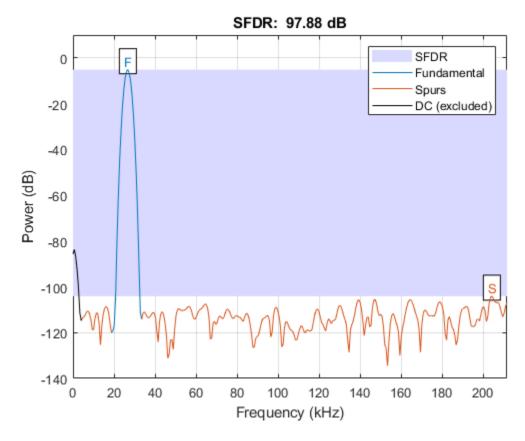

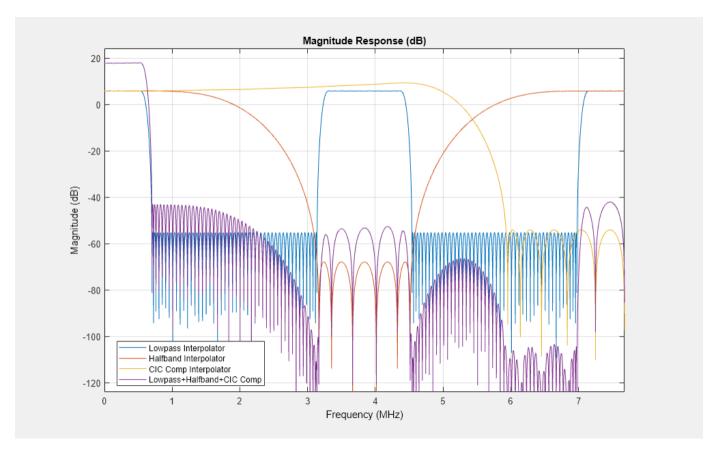

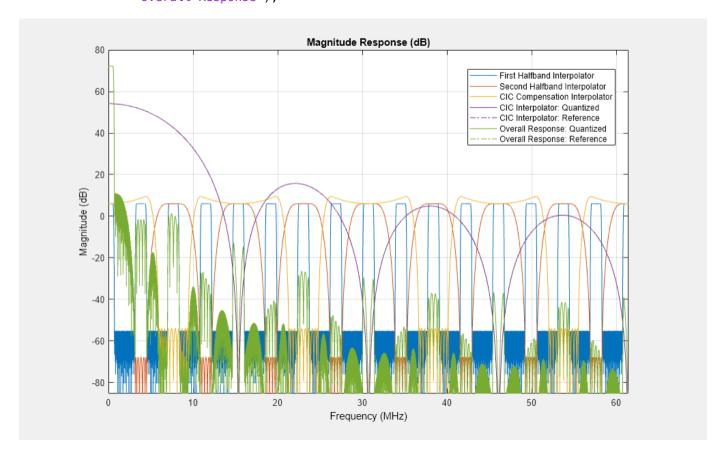

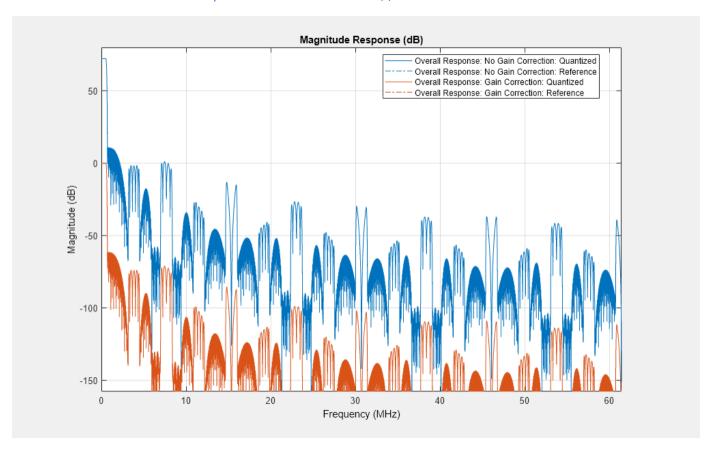

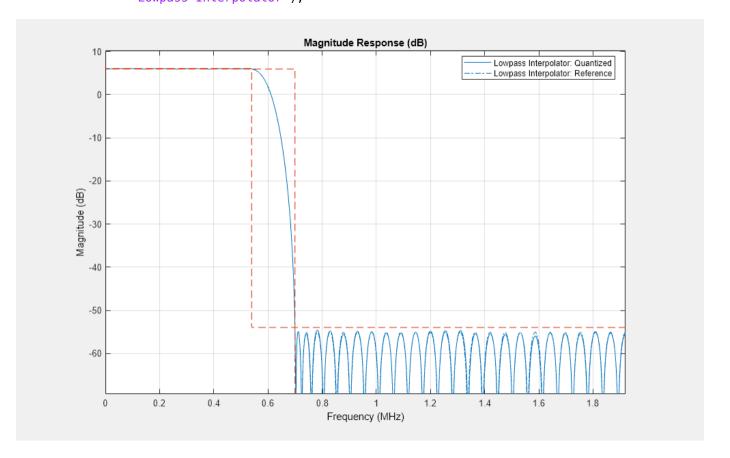

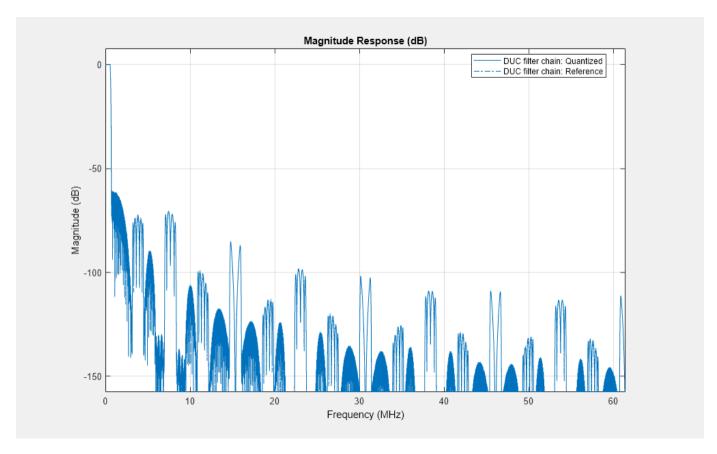

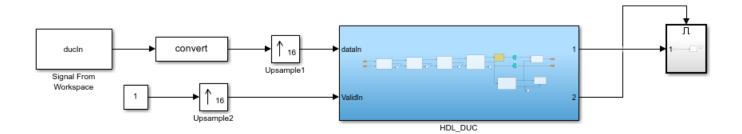

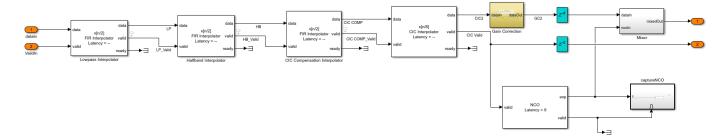

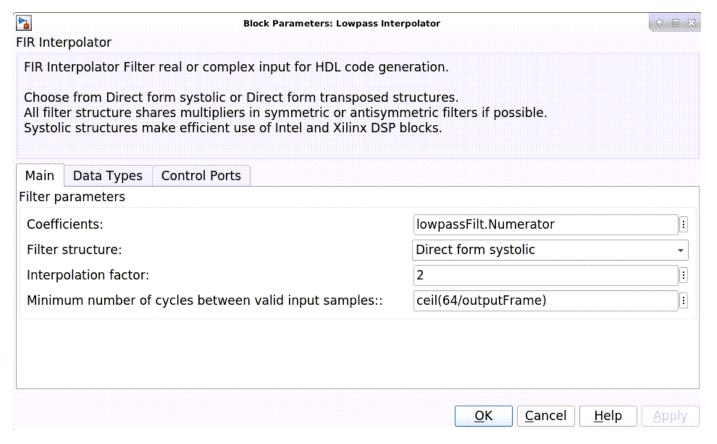

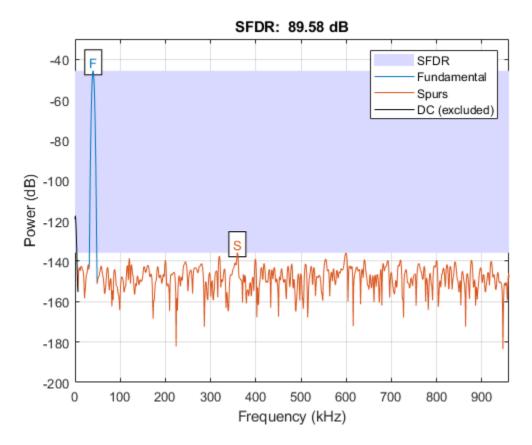

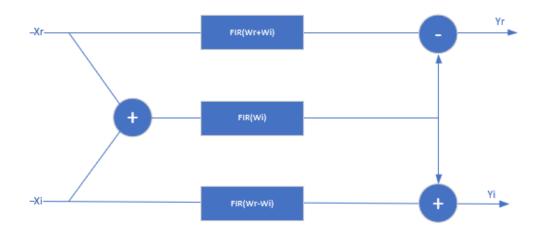

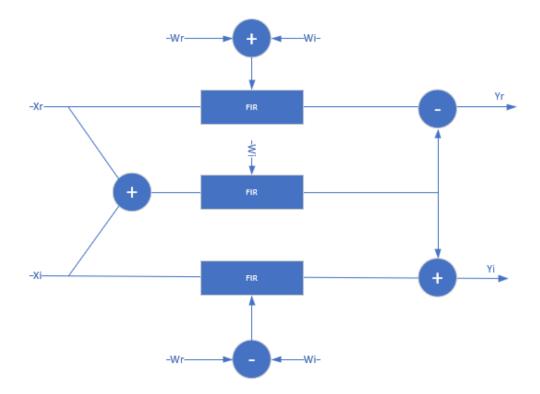

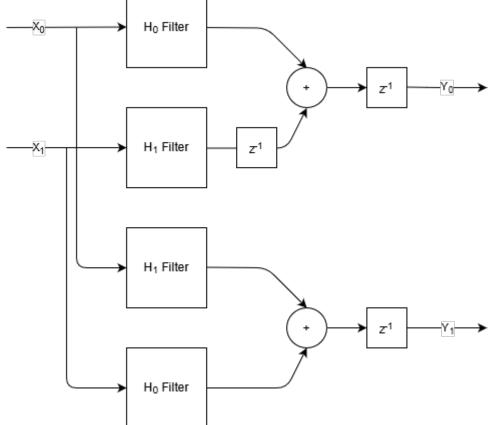

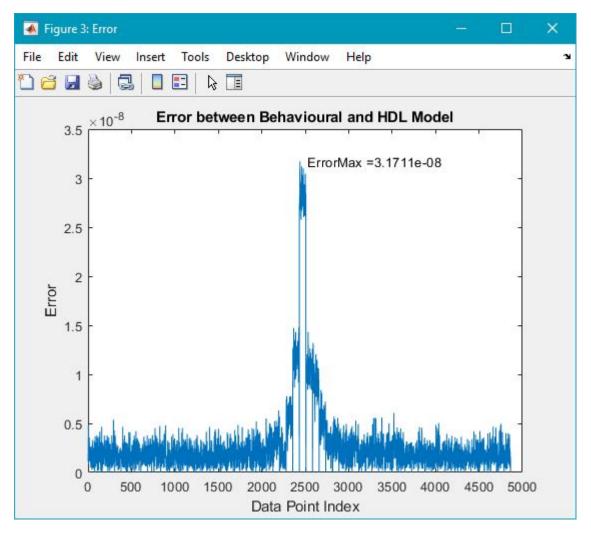

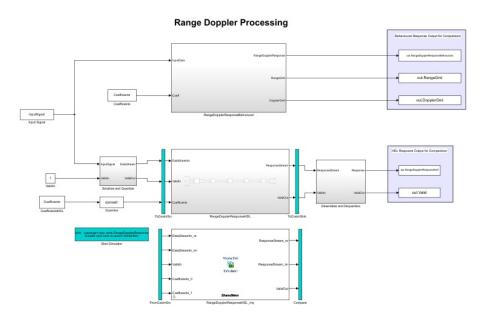

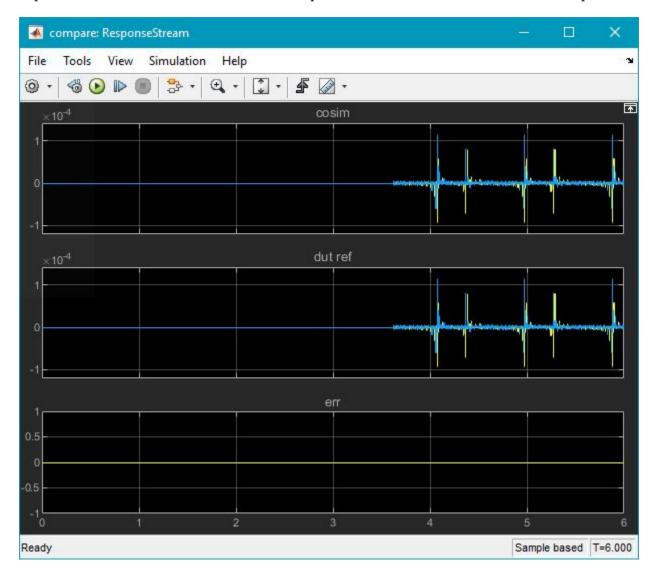

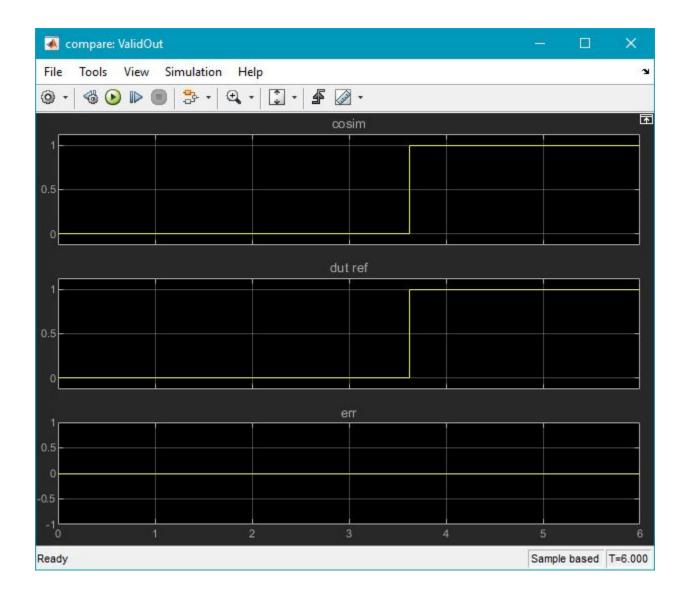

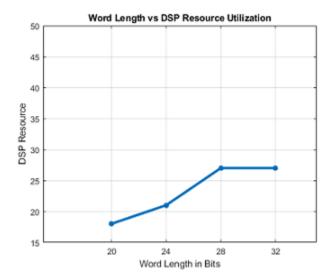

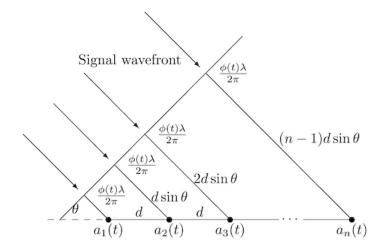

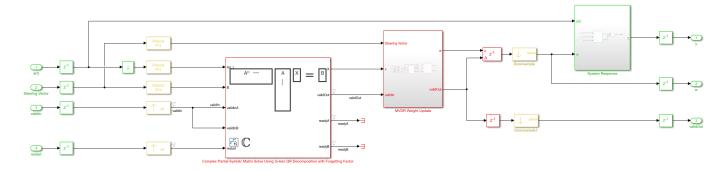

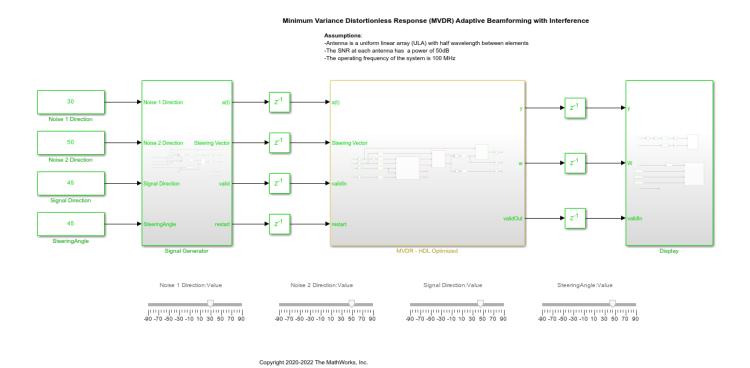

The overall response of the filter chain is equivalent to that of a single decimation filter with the same specification. However, splitting the filter into multiple decimation stages results in a more efficient design that uses fewer hardware resources.